ECL (Emitter Coupled Logic) pertama kali ditemukan di IBM pada Agustus 1956 oleh Hannon S. Yourke. Logika ini juga dikenal sebagai logika mode saat ini, digunakan di komputer IBM 7090 & 7094. Keluarga ECL sangat cepat dibandingkan dengan logika digital keluarga. Umumnya, keluarga logika ini memberikan penundaan propagasi kurang dari 1 ns. Ini adalah keluarga logika yang didasarkan pada transistor sambungan bipolar. Ini adalah rangkaian keluarga logika tercepat yang dapat diakses untuk merancang sistem logika konvensional. Artikel ini membahas ikhtisar dari sebuah emitor ditambah logika-sirkuit , bekerja dengan aplikasi.

Apa itu Logika Gabungan Emitor?

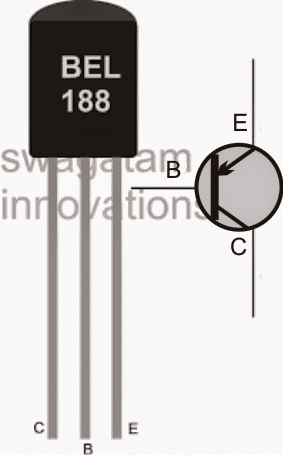

Logika berpasangan emitor adalah yang terbaik BJT keluarga logika berbasis-berbasis yang digunakan dalam desain sistem logika konvensional. Terkadang, ini juga disebut logika mode saat ini yang merupakan teknologi digital berkecepatan sangat tinggi. Secara umum, ECL dianggap sebagai IC logika tercepat di mana ia mencapai operasi kecepatan tinggi dengan menggunakan ayunan tegangan yang sangat kecil & juga menghindari transistor memasuki wilayah saturasi.

Implementasi ECL memanfaatkan tegangan suplai positif yang dikenal sebagai PECL atau ECL bereferensi positif. Pada gerbang ECL awal, suplai tegangan negatif digunakan karena kekebalan kebisingan. Setelah itu, ECL bereferensi positif menjadi sangat terkenal karena tingkat logikanya yang lebih kompatibel dibandingkan dengan keluarga logika TTL.

Logika berpasangan emitor menghilangkan sejumlah besar daya statis, namun, konsumsi arus keseluruhannya rendah dibandingkan dengan CMOS pada frekuensi tinggi. Jadi, ECL terutama bermanfaat dalam sirkuit distribusi jam & aplikasi berbasis frekuensi tinggi.

Fitur Logika Gabungan Emitor

Fitur-fitur ECL akan membuatnya digunakan di banyak aplikasi berbasis kinerja tinggi.

- ECL menyediakan dua output yang selalu saling melengkapi karena, pengoperasian rangkaian didasarkan pada penguat diferensial.

- Keluarga logika ini terutama cocok untuk metode fabrikasi monolitik karena level logika adalah fungsi dari rasio resistor.

- Perangkat dari keluarga ECL menghasilkan output yang tepat & komplementer dari fungsi yang diusulkan tanpa menggunakan inverter luar. Akibatnya, mengurangi jumlah paket, dan kebutuhan daya & juga mengurangi masalah yang terjadi dari penundaan waktu.

- Perangkat ECL dalam desain penguat diferensial menawarkan fleksibilitas kinerja yang luas, sehingga sirkuit ECL memungkinkan digunakan baik sebagai sirkuit digital maupun linier.

- Desain gerbang ECL biasanya memiliki impedansi input tinggi & rendah, yang sangat kondusif untuk mencapai kemampuan fan-out dan drive yang besar.

- Perangkat ECL menghasilkan aliran arus konstan pada catu daya untuk menyederhanakan desain catu daya.

- Perangkat ECL termasuk output emitor terbuka hanya memungkinkan mereka untuk menyertakan kapasitas drive saluran transmisi.

Sirkuit Logika Gabungan Emitor

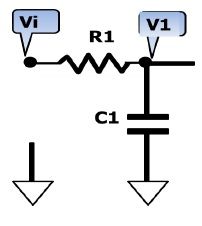

Rangkaian logika emitor-coupled untuk inverter ditunjukkan di bawah ini yang dirancang dengan resistor dan transistor. Dalam rangkaian ini, terminal emitor dari dua transistor secara sederhana dihubungkan ke resistansi pembatas arus RE yang digunakan untuk menghindari transistor masuk ke dalam saturasi. Di sini output transistor diambil dari terminal kolektor bukan dari terminal emitor. Rangkaian ini menyediakan dua output Vout (output pembalik) dan Vout2 (output non-pembalik) dan terminal input seperti Vin di mana input tinggi atau rendah diberikan. +Vcc = 5V.

Bagaimana Cara Kerja Emitter Coupled Logic?

Operasi logika emitter-coupled adalah, setiap kali input HIGH diberikan ke rangkaian ECL, maka transistor Q1 ON dan transistor Q2 OFF akan tetapi transistor Q1 tidak jenuh. Jadi ini akan menarik output VOUT2 ke HIGH dan nilai output VOUT1 akan LOW karena drop di dalam R1.

Begitu pula ketika nilai VIN yang diberikan ke ECL LOW, maka transistor Q1 akan OFF & transistor Q2 ON. Jadi, transistor Q2 tidak akan bergerak ke saturasi. Sehingga akan membuat output VOUT1 akan ditarik nilai HIGH dan nilai output VOUT2 akan menjadi rendah karena drop di dalam resistansi R2.

Mari kita lihat bagaimana transistor Q1 dan Q2 menyala dan mati ketika tegangan diberikan.

Dua transistor seperti Q1 & Q2 di sirkuit ini dihubungkan sebagai penguat diferensial oleh resistor emitor umum.

Suplai tegangan untuk rangkaian contoh ini adalah VCC = 5.0, VBB = 4.0 & VEE = 0 V. Nilai input TINGGI & RENDAH secara sederhana didefinisikan sebagai 4.4 V & 3.6V. Sebenarnya, rangkaian ini menghasilkan output LOW & HIGH level yang 0,6 Volt lebih tinggi; namun, ini dikoreksi dalam sirkuit ECL nyata.

Setelah Vin TINGGI, maka transistor Q1 dihidupkan, namun tidak jenuh & transistor Q2 dimatikan. Jadi, tegangan keluaran seperti VOUT2 ditarik ke 5 V melalui resistor R2 & dapat ditunjukkan bahwa penurunan tegangan pada resistor R1 adalah sekitar 0,8 V sehingga VOUT1 = 4,2 V (RENDAH). Selain itu VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V karena transistor Q1 ON sepenuhnya.

Setelah Vin LOW, transistor Q2 akan dihidupkan, tetapi tidak jenuh & transistor Q1 dimatikan. Oleh karena itu, VOUT1 ditarik ke 5,0 V menggunakan resistor R1 & dapat ditunjukkan bahwa VOUT2 adalah 4,2 V. Juga VE => VOUT2 – VQ2 => 4.2V – 0.8V => 3.4V karena transistor Q2 dihidupkan.

Dalam ECL, kedua transistor tidak pernah dalam keadaan jenuh karena t ayunan tegangan input / output cukup kecil seperti 0.8v dan impedansi input tinggi dan resistansi output rendah. Ini membantu ECL untuk beroperasi lebih cepat dengan waktu tunda propagasi yang lebih sedikit.

Dua Input Emitor Digabungkan Logika OR/NOR Gerbang Sirkuit

Rangkaian gerbang logika OR/NOR dua input emitor digabungkan ditunjukkan di bawah ini. Rangkaian ini dirancang dengan memodifikasi rangkaian inverter di atas. Modifikasinya adalah dengan menambahkan transistor tambahan di sisi input.

Cara kerja rangkaian ini sangat sederhana. Ketika input yang diterapkan pada transistor Q1 & Q2 rendah maka akan membuat output1 (Vout1) menjadi nilai TINGGI. Jadi, Vout1 ini sesuai dengan keluaran gerbang NOR.

Bersamaan dengan itu, jika transistor Q3 dihidupkan, maka akan membuat output kedua (Vout2) menjadi HIGH. Jadi, keluaran Vou2 ini sesuai dengan keluaran gerbang OR.

Dengan cara yang sama, jika kedua input transistor Q1 & Q2 TINGGI, maka transistor Q1 & Q2 akan menyala dan memberikan output rendah pada terminal VOUT1.

Jika transistor Q3 dimatikan selama operasi ini maka akan memberikan output tinggi di terminal VOUT2. Jadi, tabel kebenaran untuk gerbang OR/NOR diberikan di bawah ini.

|

Masukan |

Masukan | ATAU |

JUGA BUKAN |

|

SEBUAH |

B | kamu | kamu |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Karakteristik Logika Emitter-Coupled

Ciri-ciri ECL antara lain sebagai berikut.

- Dibandingkan dengan TTL, ECL memiliki waktu propagasi yang lebih cepat mulai dari 0,5 hingga 2 ns. Tapi, disipasi daya logika gabungan emitor lebih tinggi dibandingkan dengan TTL seperti 30 mW.

- Tegangan I/O ECL memiliki ayunan kecil seperti 0,8.

- Impedansi input ECL tinggi & resistansi output rendah; akibatnya, transistor mengubah statusnya dengan sangat cepat.

- Kapasitas fan-out ECL tinggi dan delay gate rendah.

- Logika output daya ECL berubah dari LOW ke HIGH tetapi level tegangan untuk status ini akan bervariasi antara TTL & EC.

- Kekebalan kebisingan ECL adalah 0.4V.

Keuntungan dan kerugian

Itu keuntungan dari logika berpasangan emitor dibahas di bawah ini.

- Fanout ECL adalah 25 yang lebih baik dibandingkan dengan TTL & rendah dibandingkan dengan CMOS.

- Waktu tunda propagasi rata-rata ECL adalah 1 hingga 4 ns yang lebih baik dibandingkan dengan CMOS &

- TTL. Oleh karena itu disebut sebagai keluarga logika tercepat.

- Ketika BJT di emitor digabungkan gerbang logika bekerja di wilayah aktif, maka mereka memiliki kecepatan maksimum dibandingkan dengan semua keluarga logika.

- Gerbang ECL menghasilkan keluaran komplementer.

- Lonjakan switching saat ini tidak ada di kabel catu daya.

- Output dapat digabungkan bersama untuk menyediakan fungsi wired-OR.

- Parameter ECL tidak banyak berubah melalui suhu.

- Tidak. fungsi yang dapat diakses dari satu-satunya chip tinggi.

Itu kelemahan logika berpasangan emitor dibahas di bawah ini.

- Ini memiliki margin kebisingan yang sangat kecil, yaitu ±200 mV.

- Disipasi daya tinggi dibandingkan dengan gerbang logika lainnya.

- Untuk berinteraksi dengan keluarga logika lainnya, pemindah level diperlukan.

- Fanout membatasi pemuatan kapasitif.

- Jika dibandingkan dengan TTL , gerbang ECL mahal.

- Dibandingkan dengan CMOS & TTL, kekebalan kebisingan ECL adalah yang terburuk.

Aplikasi

Aplikasi logika berpasangan emitor meliputi yang berikut ini.

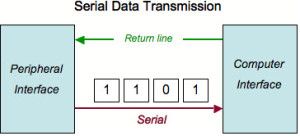

- Logika berpasangan emitor digunakan sebagai logika & teknologi antarmuka dalam perangkat komunikasi berkecepatan sangat tinggi seperti antarmuka transceiver serat optik, jaringan Ethernet & ATM (Asynchronous Transfer Mode).

- ECL adalah keluarga logika berdasarkan BJT di mana operasi kecepatan tinggi dapat dicapai dengan menggunakan ayunan tegangan yang relatif kecil & menghindari transistor bergerak ke wilayah saturasi.

- ECL digunakan dalam membuat sirkuit ASLT dalam IBM 360/91.

- ECL menghindari pemanfaatan transistor bertumpuk dengan menggunakan bias i/p ujung tunggal & umpan balik positif antara transistor primer & sekunder untuk mencapai fungsi inverter.

- ECL digunakan dalam elektronik berkecepatan sangat tinggi.

Jadi, ini adalah ikhtisar logika gabungan emitor atau ECL – sirkuit, kerja, fitur, karakteristik, dan aplikasi. ECL adalah keluarga logika tercepat berdasarkan BJT dibandingkan dengan keluarga logika digital lainnya. Ini mencapai operasi kecepatan maksimum dengan menggunakan ayunan tegangan kecil & menghindari transistor bergerak ke wilayah saturasi. Keluarga logika ini memberikan penundaan propagasi 1ns yang luar biasa dan dalam keluarga ECL terbaru, penundaan ini berkurang. Ini pertanyaan untuk Anda, apa nama alternatif untuk ECL?