Meningkatkan kecepatan eksekusi program secara konsekuen meningkatkan kecepatan prosesor. Ada banyak cara yang ditemukan, baik implementasi perangkat keras dan arsitektur perangkat lunak, untuk meningkatkan kecepatan eksekusi. Telah diamati bahwa dengan menjalankan instruksi secara bersamaan waktu yang dibutuhkan untuk eksekusi dapat dikurangi. Konsep Paralelisme dalam pemrograman diusulkan. Menurut ini, lebih dari satu instruksi dapat dieksekusi per siklus clock. Konsep ini dapat dipraktekkan oleh seorang programmer melalui berbagai teknik seperti Pipelining, Beberapa unit eksekusi, dan banyak inti . Di antara semua metode paralelisme ini, pipelining adalah yang paling umum dipraktikkan. Jadi bagaimana instruksi dapat dieksekusi dalam metode pipelining? Bagaimana cara meningkatkan kecepatan eksekusi?

Apa itu Pipelining?

Untuk memahami konsep pipelining, mari kita lihat level root bagaimana program dijalankan. Instruksi adalah paket eksekusi terkecil dari sebuah program. Setiap instruksi berisi satu atau lebih operasi. Prosesor skalar sederhana menjalankan satu atau lebih instruksi per siklus clock, dengan setiap instruksi hanya berisi satu operasi. Instruksi dijalankan sebagai urutan tahapan, untuk menghasilkan hasil yang diharapkan. Urutan ini diberikan di bawah ini

Urutan Eksekusi Instruksi

- JIKA: Mengambil instruksi ke dalam register instruksi.

- ID: Instruction Decode, menerjemahkan instruksi untuk opcode.

- AG: Address Generator, menghasilkan alamat.

- DF: Pengambilan Data, mengambil operan ke dalam register data.

- EX: Eksekusi, menjalankan operasi yang ditentukan.

- WB: Tulis kembali, tulis kembali hasilnya ke pendaftaran.

Tidak semua instruksi memerlukan semua langkah di atas tetapi kebanyakan membutuhkan. Langkah-langkah ini menggunakan fungsi perangkat keras yang berbeda. Dalam pipelining, fase yang berbeda ini dilakukan secara bersamaan. Dalam pipelining, fase-fase ini dianggap independen antara operasi yang berbeda dan dapat saling tumpang tindih. Dengan demikian, beberapa operasi dapat dilakukan secara bersamaan dengan setiap operasi berada dalam fase independennya sendiri.

Pipelining Instruksi

Mari kita lihat bagaimana instruksi diproses dalam pipelining. Ini dapat dengan mudah dipahami dengan diagram di bawah ini.

Pipelining Instruksi

Asumsikan bahwa instruksi tersebut independen. Dalam prosesor pipelining sederhana, pada waktu tertentu, hanya ada satu operasi di setiap fase. Fase awal adalah fase IF. Jadi, pada siklus jam pertama, satu operasi diambil. Ketika pulsa clock berikutnya tiba, operasi pertama masuk ke fase ID meninggalkan fase IF kosong. Sekarang, fase kosong ini dialokasikan ke operasi berikutnya. Jadi, selama pulsa clock kedua, operasi pertama berada di fase ID dan operasi kedua di fase IF.

Untuk siklus ketiga, operasi pertama di fase AG, operasi kedua di fase ID dan operasi ketiga di fase IF. Dengan cara ini, instruksi dieksekusi secara bersamaan dan setelah enam siklus prosesor akan mengeluarkan instruksi yang dieksekusi secara lengkap per siklus clock.

Apakah instruksi ini telah dijalankan secara berurutan, awalnya instruksi pertama harus melalui semua tahapan kemudian instruksi berikutnya akan diambil? Jadi, untuk mengeksekusi setiap instruksi, prosesor membutuhkan enam siklus clock. Tetapi dalam prosesor pipelined karena eksekusi instruksi berlangsung secara bersamaan, hanya instruksi awal yang memerlukan enam siklus dan semua instruksi yang tersisa dieksekusi sebagai satu per setiap siklus sehingga mengurangi waktu eksekusi dan meningkatkan kecepatan prosesor.

Arsitektur Pipelining

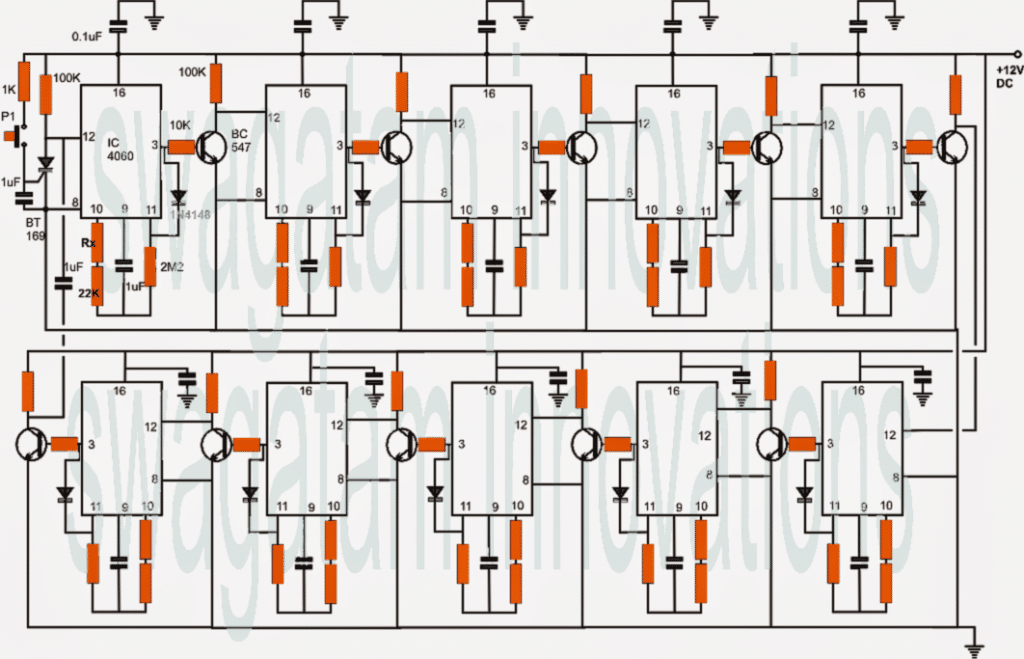

Paralelisme dapat dicapai dengan teknik Hardware, Compiler, dan software. Untuk memanfaatkan konsep pipelining in Arsitektur komputer banyak unit prosesor yang saling berhubungan dan berfungsi secara bersamaan. Dalam arsitektur prosesor pipelined, terdapat unit pemrosesan terpisah yang disediakan untuk instruksi integer dan floating point. Sedangkan dalam arsitektur sekuensial, disediakan satu unit fungsional.

Unit Prosesor Pipa

Dalam pipelining statis, prosesor harus meneruskan instruksi melalui semua fase pipeline terlepas dari persyaratan instruksi. Dalam prosesor pipeline dinamis, instruksi dapat melewati fase tergantung pada kebutuhannya tetapi harus bergerak secara berurutan. Dalam prosesor pipa dinamis yang kompleks, instruksi dapat melewati fase serta memilih fase yang tidak berurutan.

Pipelining di Prosesor RISC

Yang paling populer Arsitektur RISC Prosesor ARM mengikuti pipelining 3-tahap dan 5-tahap. Pada pipelining 3 tahap tahapannya adalah: Fetch, Decode, dan Execute. Pipelining ini memiliki latensi 3 siklus, karena setiap instruksi membutuhkan 3 siklus clock untuk menyelesaikannya.

Pipelining tahap ARM 3

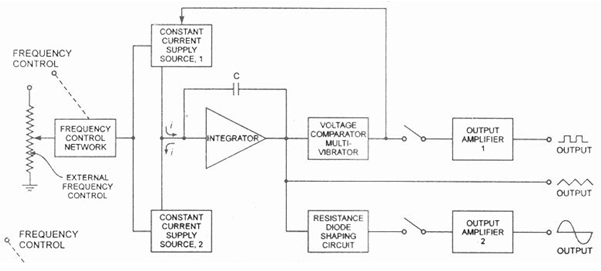

Untuk implementasi yang tepat dari arsitektur perangkat keras pipelining juga harus ditingkatkan. Perangkat keras untuk pipelining 3 tahap termasuk bank register, ALU, Barrel shifter, Address generator, incrementer, Instruction decoder, dan data register.

Datapath Pipelining Tahap 3 ARM

Dalam 5 tahapan pipelining tahapannya adalah: Fetch, Decode, Execute, Buffer / data dan Write back.

Bahaya Pipelining

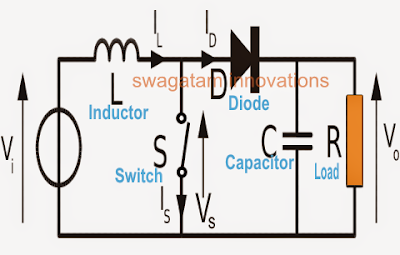

Dalam program komputer tipikal selain instruksi sederhana, ada instruksi cabang, operasi interupsi, instruksi baca dan tulis. Pipelining tidak cocok untuk semua jenis instruksi. Ketika beberapa instruksi dijalankan dalam pipelining, mereka dapat menghentikan pipeline atau membilasnya secara total. Jenis masalah yang disebabkan selama pemipaan disebut Bahaya Pemipaan.

Di sebagian besar program komputer, hasil dari satu instruksi digunakan sebagai operand oleh instruksi lainnya. Ketika instruksi tersebut dijalankan dalam pipelining, kerusakan terjadi karena instruksi pertama tidak tersedia ketika instruksi dua mulai mengumpulkan operan. Jadi, instruksi dua harus berhenti sampai instruksi satu dijalankan dan hasilnya dihasilkan. Jenis bahaya ini disebut bahaya pemipaan Baca-setelah-tulis.

Baca Setelah Menulis Bahaya Pipelining

Pelaksanaan instruksi cabang juga menyebabkan bahaya pipelining. Instruksi cabang saat dijalankan di pipelining mempengaruhi tahap pengambilan dari instruksi selanjutnya.

Perilaku Cabang Pipelined

Keuntungan Pipelining

- Throughput instruksi meningkat.

- Peningkatan jumlah tahapan pipeline meningkatkan jumlah instruksi yang dijalankan secara bersamaan.

- ALU yang lebih cepat dapat dirancang saat pipelining digunakan.

- CPU Pipelined bekerja pada frekuensi clock yang lebih tinggi daripada RAM.

- Pipelining meningkatkan kinerja CPU secara keseluruhan.

Kerugian dari Pipelining

- Merancang prosesor pipelined itu rumit.

- Latensi instruksi meningkat dalam prosesor pipelined.

- Throughput prosesor pipelined sulit untuk diprediksi.

- Semakin panjang pipa, semakin buruk masalah bahaya untuk instruksi cabang.

Pipelining memanfaatkan semua instruksi yang mengikuti urutan langkah yang serupa untuk eksekusi. Prosesor yang memiliki instruksi kompleks di mana setiap instruksi berperilaku berbeda dari yang lain sulit untuk disalurkan. Prosesor memiliki implementasi yang wajar dengan 3 atau 5 tahap pipa karena semakin dalam pipa meningkatkan bahaya yang terkait dengannya meningkat. Sebutkan beberapa prosesor jalur pipa dengan tahap jalur pipa mereka?