Dua jenis utama FET yang saat ini ada adalah: JFET dan MOSFET.

MOSFET dapat diklasifikasikan lebih lanjut menjadi tipe deplesi dan jenis peningkatan. Kedua jenis ini menentukan mode dasar operasi MOSFET, sedangkan istilah MOSFET itu sendiri adalah singkatan dari transistor efek medan-oksida-logam-semikonduktor.

Karena kedua jenis memiliki karakteristik kerja yang berbeda, kami akan mengevaluasi masing-masing secara terpisah di artikel yang berbeda.

Perbedaan antara Enhancement dan Deplesion MOSFET

Pada dasarnya, tidak seperti MOSFET peningkatan, MOSFET deplesi berada dalam status on-state bahkan dengan adanya 0 V melintasi terminal gate-to-source (VGS).

Untuk peningkatan MOSFET, tegangan gerbang-ke-sumber (VGS) harus di atas tegangan ambang gerbang-ke-sumber (VGS (th)) untuk membuatnya berjalan .

Namun, untuk MOSFET deplesi saluran-N, nilai VGS (th) di atas 0 V. Ini berarti bahwa meskipun VGS = 0 V, MOSFET deplesi dapat menghantarkan arus. Untuk mematikannya, VGS dari deplesi MOSFET perlu dikurangi di bawah VGS (th) (negatif).

Pada artikel kali ini kita akan membahas jenis deplesi MOSFET, yang dikatakan memiliki karakteristik yang cocok dengan JFET. Kesamaannya adalah antara cut-off dan saturation dekat IDSS.

Konstruksi Dasar

Gbr. 5.23 menunjukkan struktur internal dasar dari MOSFET tipe deplesi saluran-n.

Kita dapat menemukan blok bahan tipe-p yang dibuat dengan menggunakan basis silikon. Blok ini disebut substrat.

Substrat adalah alas atau pondasi tempat MOSFET dibangun. Untuk beberapa MOSFET, MOSFET terhubung secara internal dengan terminal 'sumber'. Selain itu, banyak perangkat menawarkan output tambahan dalam bentuk SS, yang menampilkan MOSFET 4 terminal, seperti yang terungkap pada Gambar 5.23

Saluran pembuangan dan terminal sumber dihubungkan melalui kontak konduktif ke lokasi n-doped, dan dipasang melalui saluran-n, seperti yang ditunjukkan pada gambar yang sama.

Gerbang juga terhubung ke lapisan logam, meskipun diisolasi dari saluran-n melalui lapisan silikon dioksida (SiOdua).

SiOduamemiliki bentuk unik dari sifat isolasi yang disebut dielektrik yang menciptakan medan listrik berlawanan dalam dirinya sendiri sebagai respons terhadap medan listrik yang diterapkan secara eksternal.

Menjadi lapisan isolasi, material SiOduamemberi kami informasi penting berikut:

Isolasi lengkap dikembangkan antara terminal gerbang dan saluran MOSFET dengan bahan ini.

Apalagi karena SiOdua, gerbang MOSFET mampu menampilkan tingkat impedansi masukan yang sangat tinggi.

Karena properti impedansi input tinggi yang vital ini, arus gerbang IGhampir nol amp untuk konfigurasi MOSFET bias-dc.

Operasi dan Karakteristik Dasar

AS dapat dilihat pada Gambar 5.24, tegangan gerbang ke sumber telah dikonfigurasi pada nol volt dengan menghubungkan kedua terminal bersama-sama, sedangkan tegangan VDSditerapkan di saluran pembuangan dan terminal sumber.

Dengan pengaturan di atas, sisi pembuangan membentuk potensial positif oleh elektron bebas saluran-n, bersama dengan arus ekivalen melalui saluran JFET. Juga, arus yang dihasilkan VGS= 0V masih diidentifikasi sebagai IDSS, seperti yang diberikan pada Gambar 5.25

Kita dapat melihat bahwa pada Gambar 5.26 tegangan sumber gerbang VGSdiberi potensi negatif dalam bentuk -1V.

Potensial negatif ini mencoba untuk memaksa elektron menuju substrat saluran-p (karena muatan menolak), dan menarik lubang dari substrat saluran-p (karena muatan berlawanan menarik).

Tergantung seberapa besar bias negatif ini VGSadalah, rekombinasi lubang dan elektron terjadi yang menghasilkan reduksi elektron bebas di saluran-n yang tersedia untuk konduksi. Tingkat bias negatif yang lebih tinggi menghasilkan tingkat rekombinasi yang lebih tinggi.

Alhasil, arus drain berkurang dengan meningkatnya kondisi bias negatif di atas, yang dibuktikan pada Gambar 5.25 untuk VGStingkat VGS= -1, -2 dan seterusnya, hingga tanda pinch-off -6V.

Aliran drain sebagai akibatnya bersama dengan plot kurva transfer berjalan seperti pada a JFET.

Sekarang, untuk V positifGSnilai-nilai, gerbang positif akan menarik elektron berlebih (pembawa bebas) dari substrat tipe-p, karena arus bocor terbalik. Ini akan membentuk pembawa baru melalui tumbukan yang dihasilkan di seluruh partikel yang dipercepat.

Karena tegangan gerbang-ke-sumber cenderung naik pada laju positif, arus drain menunjukkan peningkatan yang cepat, seperti yang dibuktikan pada Gambar 5.25 untuk alasan yang sama seperti yang dibahas di atas.

Kesenjangan dikembangkan antara kurva VGS= 0V dan V.GS= +1 secara jelas menunjukkan jumlah dimana arus meningkat karena variasi 1 - V dari VGS

Karena kenaikan cepat arus drain, kita harus berhati-hati tentang peringkat arus maksimum, jika tidak maka dapat melewati batas tegangan gerbang positif.

Misalnya, untuk tipe perangkat yang digambarkan pada Gbr.5.25, menerapkan VGS= + 4V akan menyebabkan arus drain naik pada 22,2 mA, yang mungkin melewati batas kerusakan maksimum (arus) perangkat.

Kondisi di atas menunjukkan bahwa penggunaan tegangan gerbang-ke-sumber positif menghasilkan efek yang ditingkatkan pada jumlah pembawa bebas di saluran, berlawanan dengan ketika VGS= 0V.

Inilah sebabnya mengapa daerah tegangan gerbang positif pada drain atau karakteristik transfer umumnya dikenal sebagai wilayah peningkatan . Wilayah ini terletak di antara titik potong dan tingkat kejenuhan IDSSatau wilayah penipisan.

Memecahkan Masalah Contoh

Keuntungan dan Aplikasi

Berbeda dengan MOSFET mode-peningkatan, di mana kami menemukan arus drain turun ke nol sebagai respons terhadap tegangan gerbang-ke-sumber nol, FET mode-deplesi modern menampilkan arus yang nyata dengan tegangan gerbang nol. Tepatnya, resistansi drain-to-source biasanya 100 Ohm dalam tegangan nol.

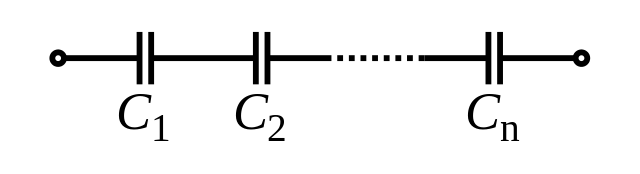

Seperti yang ditunjukkan pada grafik di atas, rds resistansi ON(di)vs kisaran sinyal analog terlihat seperti respon yang praktis datar. Karakteristik ini, dalam hubungannya dengan tingkat kapasitansi rendah dari perangkat tipe deplesi lanjutan ini, memungkinkannya untuk secara khusus ideal sebagai sakelar analog untuk aplikasi pengalihan audio dan video.

Atribut 'normal-on' MOSFET mode-deplesi memungkinkan perangkat menjadi sangat cocok untuk regulator arus FET tunggal.

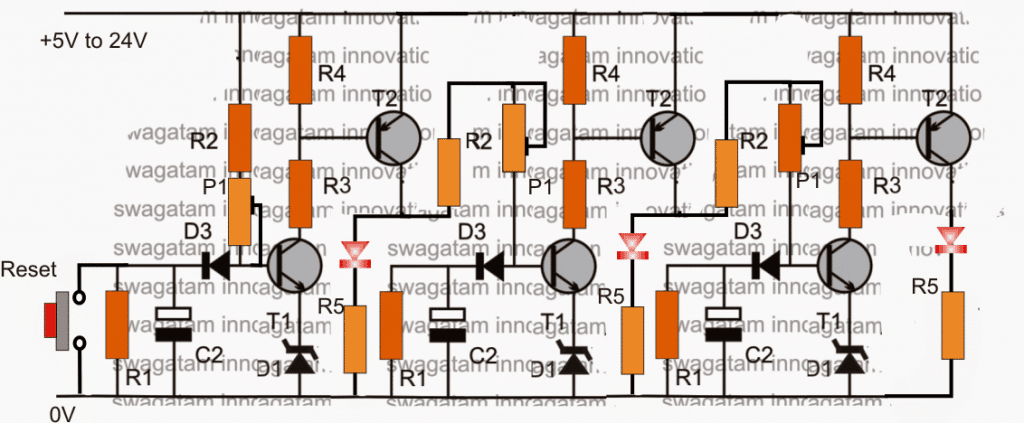

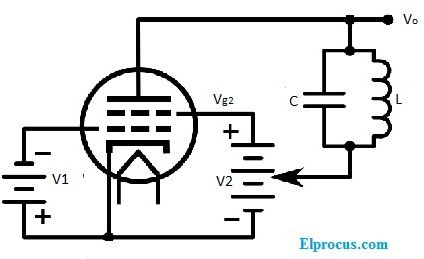

Salah satu contoh rangkaian tersebut dapat dilihat pada gambar berikut.

Nilai Rs dapat ditentukan dengan rumus:

Rs= VGSmati[1 - (SayaD/SAYADSS)1/2] / SayaD

dimana sayaD adalah jumlah arus yang diatur yang diperlukan pada keluaran.

Keuntungan utama dari MOSFET mode-deplesi dalam aplikasi sumber-arus adalah kapasitansi pembuangannya yang minimal, yang membuatnya sesuai untuk aplikasi biasing dalam sirkuit kebocoran input rendah, kecepatan sedang (> 50 V / us).

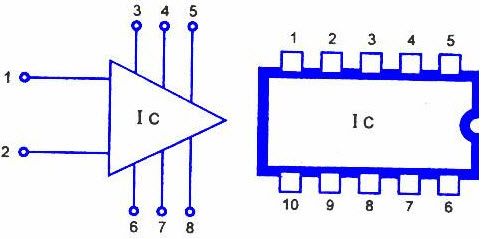

Gambar di bawah ini menunjukkan front-end diferensial arus masuk-kebocoran rendah menggunakan fungsi FET kebocoran rendah ganda.

Secara umum, kedua sisi JFET akan menjadi bias pada ID = 500 uA. Oleh karena itu, arus yang dapat diperoleh untuk mengisi kompensasi dan kapasitansi tersesat menjadi terbatas pada 2ID atau, dalam kasus seperti ini, 1,0 mA. Fitur terkait JFET telah terbukti produksi dan dijamin di lembar data.

Cs melambangkan kapasitansi keluaran dari sumber arus 'ekor' tahap masukan. Kapasitansi ini sangat penting dalam penguat non-pembalik, karena fakta bahwa tahap input mengalami pertukaran sinyal yang signifikan di seluruh jaringan ini, dan arus pengisian di Cs bisa jadi besar. Jika sumber arus normal digunakan, kapasitansi ekor ini dapat dipertanggungjawabkan untuk penurunan laju perubahan tegangan yang nyata pada rangkaian non-pembalik (dibandingkan dengan aplikasi pembalik, di mana arus pengisian dalam Cs cenderung minimal).

Penurunan laju perubahan tegangan dapat dinyatakan sebagai:

1 / 1+ (Cs / Sc)

Selama Cs lebih rendah dari Cc (kapasitor kompensasi), hampir tidak ada variasi dalam laju perubahan tegangan. Bekerja dengan DMOS FET, Cs bisa menjadi sekitar 2 pF. Strategi ini menghasilkan peningkatan besar dalam laju perubahan tegangan. Di mana defisit arus lebih tinggi dari 1 hingga 5 mA diperlukan, perangkat dapat dibiaskan ke mode peningkatan untuk menghasilkan sebanyak 20 mA untuk VGS maksimum +2,5 V, dengan kapasitansi keluaran minimal terus menjadi aspek kunci.

Aplikasi berikutnya di bawah ini menunjukkan rangkaian sumber arus mode-peningkatan yang tepat.

Sakelar analog 'normal-on' dapat dibangun untuk persyaratan di mana kondisi standar menjadi diperlukan selama kegagalan tegangan suplai, misalnya dalam rentang otomatis alat uji atau untuk memastikan start-up yang akurat dari rangkaian logika pada sakelar ON.

Tegangan ambang negatif yang berkurang dari perangkat menawarkan prasyarat dasar penggerak dan izin bekerja dengan tegangan minimal.

Rangkaian di bawah ini menunjukkan faktor bias umum untuk sakelar analog DMOS mode-deplesi.

Untuk menyebabkan perangkat mati, tegangan negatif diperlukan di gerbang. Karena itu, on-resistance dapat diminimalkan ketika FET juga ditingkatkan menggunakan tegangan gerbang positif, memungkinkannya secara khusus di wilayah mode-peningkatan bersama dengan wilayah mode-penipisan.

Respon tersebut dapat disaksikan pada grafik berikut.

Penguatan frekuensi tinggi dari unit, bersama dengan nilai kapasitansi rendahnya, menghasilkan peningkatan 'gambaran jasa'. Ini benar-benar elemen penting dalam amplifikasi VHF dan UHF, yang menentukan produk gain-bandwidth (GBW) dari FET, yang dapat digambarkan sebagai:

GBW = gfs / 2 Pi (Cdi+ Cdi luar)

p-Channel Deplesion-Type MOSFET

Konstruksi MOSFET tipe deplesi kanal-p adalah kebalikan sempurna dari versi kanal-n yang ditunjukkan pada Gbr. 5.23. Artinya, substrat tersebut sekarang berbentuk tipe-n dan salurannya menjadi tipe-p, seperti dapat dilihat pada Gambar 5.28a di bawah ini.

Identifikasi terminal tetap tidak berubah, tetapi tegangan dan polaritas arus dibalik, seperti yang ditunjukkan pada gambar yang sama. Karakteristik saluran pembuangan akan persis seperti yang digambarkan pada Gambar 5.25, kecuali V.DStanda yang dalam hal ini akan mendapatkan nilai negatif.

Arus drain IDmenunjukkan polaritas positif dalam kasus ini juga, itu karena kami telah membalikkan arahnya. V.GSmenunjukkan polaritas yang berlawanan, yang dapat dimengerti, seperti yang ditunjukkan pada Gambar 5.28c.

Karena VGSdibalik menghasilkan bayangan cermin untuk karakteristik transfer seperti yang ditunjukkan pada Gambar.5,28b.

Artinya, arus drain meningkat pada V positifGSwilayah dari titik potong di VGS= Vp sampai sayaDSS, kemudian terus naik sebagai nilai negatif dari VGSnaik.

Simbol

Tanda-tanda grafis untuk MOSFET tipe deplesi kanal-n dan p-channel dapat dilihat pada Gambar 5.29 di atas.

Amati cara simbol yang dipilih bertujuan untuk mewakili struktur perangkat yang sebenarnya.

Tidak adanya interkoneksi langsung (karena isolasi gerbang) antara gerbang dan saluran dilambangkan dengan celah antara gerbang dan terminal simbol yang berbeda.

Garis vertikal yang mewakili saluran dipasang di antara saluran pembuangan dan sumber dan 'dipegang' oleh substrat.

Dalam gambar di atas, terdapat dua kelompok simbol untuk setiap jenis saluran guna menyoroti fakta bahwa di beberapa perangkat, media dapat diakses secara eksternal sementara di perangkat lain hal ini mungkin tidak terlihat.

MOSFET (Tipe Peningkatan)

Meskipun MOSFET tipe deplesi dan tipe peningkatan terlihat serupa dengan struktur internal dan mode fungsionalnya, karakteristiknya mungkin sangat berbeda.

Perbedaan utama adalah arus drain yang bergantung pada tingkat tegangan gerbang-ke-sumber tertentu untuk aksi cut off.

Tepatnya, MOSFET tipe peningkatan saluran n dapat bekerja dengan tegangan gerbang / sumber positif, alih-alih rentang potensial negatif yang biasanya dapat memengaruhi MOSFET jenis penipisan.

Konstruksi Dasar

Anda dapat memvisualisasikan MOSFET jenis perangkat tambahan n-channel berikut ini

Gambar 5.31.

Bagian bahan tipe-p dibuat melalui basis silikon, dan seperti yang telah dipelajari sebelumnya disebut sebagai substrat.

Substrat ini pada beberapa kesempatan dipasang secara internal dengan pin sumber dalam MOSFET tipe penipisan, sementara dalam beberapa kasus itu diakhiri sebagai lead keempat untuk mengaktifkan kontrol eksternal pada level potensinya.

Terminal sumber dan saluran pembuangan seperti biasa disambungkan menggunakan kontak logam ke daerah n-doped.

Namun, mungkin penting untuk memvisualisasikan bahwa pada Gambar 5.31 saluran antara dua daerah doped hilang.

Hal ini dapat dianggap sebagai ketidaksamaan mendasar antara tata letak internal MOSFET jenis penipisan dan jenis perangkat tambahan, yaitu tidak adanya saluran yang melekat yang seharusnya menjadi bagian dari perangkat.

Lapisan SiO2 masih terlihat umum, yang memastikan isolasi antara dasar logam terminal gerbang dan wilayah antara saluran dan sumber. Namun, di sini bisa disaksikan berdiri terpisah dari bagian material tipe-p.

Dari pembahasan di atas kita dapat menyimpulkan bahwa deplesi dan peningkatan MOSFET tata letak internal mungkin memiliki beberapa kesamaan, kecuali saluran yang hilang antara saluran / sumber untuk jenis peningkatan MOSFET.

Operasi dan Karakteristik Dasar

Untuk jenis peningkatan MOSFET ketika 0 V diperkenalkan pada VGS-nya, karena saluran-n yang hilang (yang diketahui membawa banyak pembawa bebas) menyebabkan keluaran saat ini menjadi nol, yang sangat berbeda dari jenis penipisan dari MOSFET, memiliki ID = IDSS.

Dalam situasi seperti itu karena jalur yang hilang melintasi terminal drain / source, sejumlah besar pembawa dalam bentuk elektron tidak dapat terakumulasi di drain / source (karena daerah n-doped).

Menerapkan beberapa potensi positif di VDS, dengan VGS diatur pada nol volt dan terminal SS disingkat dengan terminal sumber, kami benar-benar menemukan beberapa persimpangan pn bias balik antara daerah n-doped dan substrat-p untuk mengaktifkan konduksi penting di seluruh tiriskan ke sumber.

Pada Gambar 5.32 menunjukkan kondisi di mana VDS dan VGS diterapkan dengan beberapa tegangan positif lebih tinggi dari 0 V, memungkinkan drain dan gerbang berada pada potensial positif sehubungan dengan sumbernya.

Potensi positif di pintu gerbang mendorong lubang pada substrat-p di sepanjang tepi lapisan SiO2 meninggalkan lokasi dan masuk lebih dalam ke wilayah substrat-p, seperti yang ditunjukkan pada gambar di atas. Hal ini terjadi karena adanya dakwaan sejenis yang saling tolak.

Ini menghasilkan daerah penipisan yang dibuat dekat dengan lapisan isolasi SiO2 yang tidak memiliki lubang.

Meskipun demikian, elektron substrat-p yang merupakan pembawa minoritas material ditarik ke arah gerbang positif dan mulai berkumpul di wilayah yang dekat dengan permukaan lapisan SiO2.

Karena sifat isolasi pembawa negatif lapisan SiO2 memungkinkan pembawa negatif terserap di terminal gerbang.

Saat kita meningkatkan level VGS, kerapatan elektron yang dekat dengan permukaan SiO2 juga meningkat, sampai akhirnya daerah tipe-n yang diinduksi dapat memungkinkan konduksi yang dapat diukur melintasi drain / source.

Besarnya VGS yang menyebabkan peningkatan optimal pada arus drain disebut sebagai tegangan ambang, ditandai dengan simbol VT . Dalam lembar data Anda akan dapat melihat ini sebagai VGS (Th).

Seperti yang dipelajari di atas, karena tidak adanya saluran pada VGS = 0, dan 'ditingkatkan' dengan aplikasi tegangan gerbang-ke-sumber positif, jenis MOSFET ini dikenal sebagai MOSFET tipe peningkatan.

Anda akan menemukan bahwa MOSFET tipe penipisan dan peningkatan menunjukkan wilayah tipe peningkatan, tetapi istilah peningkatan digunakan untuk yang terakhir karena secara khusus bekerja menggunakan mode operasi penyempurnaan.

Sekarang, ketika VGS didorong melewati nilai ambang batas, konsentrasi pembawa bebas akan meningkat di saluran tempat ia diinduksi. Hal ini menyebabkan arus drain meningkat.

Di sisi lain, jika kita menjaga VGS konstan dan meningkatkan level VDS (drain-to-source voltage), ini pada akhirnya akan menyebabkan MOSFET mencapai titik jenuhnya, seperti biasanya juga akan terjadi pada JFET atau deplesi MOSFET.

Seperti yang ditunjukkan pada Gambar 5.33 ID arus drain akan diratakan dengan bantuan proses pinching-off, yang ditunjukkan oleh saluran yang lebih sempit menuju ujung drain dari saluran induksi.

Dengan menerapkan hukum tegangan Kirchhoff ke tegangan terminal MOSFET pada Gambar 5.33, kita mendapatkan:

Jika VGS dijaga konstan ke nilai tertentu, misalnya 8 V, dan VDS dinaikkan dari 2 menjadi 5 V, tegangan VDG oleh Persamaan. 5.11 terlihat turun dari -6 ke -3 V, dan potensi gerbang semakin kurang positif sehubungan dengan tegangan drain.

Respon ini melarang pembawa bebas atau elektron ditarik ke arah wilayah saluran induksi ini, yang pada gilirannya mengakibatkan penurunan lebar efektif saluran.

Pada akhirnya, lebar saluran berkurang ke titik pinch-off, mencapai kondisi saturasi yang serupa dengan apa yang telah kita pelajari di artikel MOSFET penipisan sebelumnya.

Artinya, meningkatkan VDS lebih jauh dengan VGS tetap tidak mempengaruhi tingkat kejenuhan ID, sampai titik di mana situasi kerusakan tercapai.

Melihat Gambar 5.34 kita dapat mengidentifikasi bahwa untuk MOSFET seperti pada Gambar 5.33 yang memiliki VGS = 8 V, saturasi terjadi pada level VDS 6 V. Tepatnya, level saturasi VDS dikaitkan dengan level VGS yang diterapkan oleh:

Tidak diragukan lagi, hal ini menyiratkan bahwa ketika nilai VT ditetapkan, meningkatkan level VGS secara proporsional akan menyebabkan level saturasi yang lebih tinggi untuk VDS melalui lokus level saturasi.

Mengacu pada karakteristik yang ditunjukkan pada gambar di atas, level VT adalah 2 V, yang dibuktikan dengan fakta bahwa arus drain telah turun menjadi 0 mA.

Oleh karena itu biasanya kami dapat mengatakan:

Jika nilai VGS kurang dari ambang batas untuk MOSFET tipe peningkatan, arus drainnya adalah 0 mA.

Kita juga dapat melihat dengan jelas pada gambar di atas bahwa selama VGS dinaikkan lebih tinggi dari VT ke 8 V, tingkat saturasi yang sesuai untuk ID juga meningkat dari 0 menjadi 10 mA.

Selain itu, kita dapat melihat lebih lanjut bahwa jarak antara level VGS meningkat dengan peningkatan nilai VGS, menyebabkan kenaikan arus drain yang tak terbatas.

Kami menemukan nilai arus drain terkait dengan tegangan gerbang-ke-sumber untuk level VGS yang lebih besar dari VT, melalui hubungan nonlinier berikut:

Istilah yang ditampilkan braket kuadrat adalah istilah yang bertanggung jawab atas hubungan nonlinier antara ID dan VGS.

Istilah k adalah konstanta dan merupakan fungsi dari tata letak MOSFET.

Kita dapat mengetahui nilai konstanta ini melalui persamaan berikut:

di mana ID (on) dan VGD (on) masing-masing adalah nilai yang secara spesifik bergantung pada karakteristik perangkat.

Pada Gambar 5.35 berikutnya di bawah ini kita menemukan karakteristik drain dan transfer diatur satu di samping yang lain untuk memperjelas proses transfer satu sama lain.

Pada dasarnya, ini mirip dengan proses yang dijelaskan sebelumnya untuk JFET dan MOSFET tipe deplesi.

Namun, untuk kasus ini kita harus ingat bahwa arus drain 0 mA untuk VGS VT.

Di sini ID dapat melihat jumlah arus yang nyata, yang akan meningkat sebagaimana ditentukan oleh Persamaan. 5.13.

Perhatikan, saat menentukan titik di atas karakteristik transfer dari karakteristik saluran, kami hanya mempertimbangkan tingkat kejenuhan. Ini membatasi wilayah operasi ke nilai VDS yang lebih tinggi dari tingkat saturasi seperti yang ditetapkan oleh Persamaan. (5.12).

MOSFET Jenis Peningkatan-Channel

Struktur MOSFET tipe peningkatan saluran-p seperti yang ditunjukkan pada Gambar 5.37a adalah kebalikan dari yang ditunjukkan pada Gambar 5.31.

Artinya,, sekarang Anda menemukan bahwa substrat tipe-n dan daerah p-doped di bawah saluran pembuangan dan sambungan sumber.

Terminal tetap seperti mapan, tetapi masing-masing arah arus dan polaritas tegangan dibalik.

Karakteristik saluran pembuangan dapat terlihat seperti yang diberikan pada Gambar 5.37c, yang memiliki jumlah arus yang meningkat yang disebabkan oleh besaran VGS yang terus menerus lebih negatif.

Karakteristik transfer akan menjadi kesan cermin (disekitar sumbu ID) dari kurva transfer pada Gambar 5.35, memiliki ID yang meningkat dengan semakin banyak nilai negatif dari VGS di atas VT, seperti yang ditunjukkan pada Gambar 5.37b. Persamaan (5.11) sampai (5.14) juga sesuai untuk perangkat p-channel.

Referensi:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Sepasang: Sirkuit Detektor RF Anti Spy - Detektor Bug Nirkabel Berikutnya: Karakteristik Transfer

![Sirkuit Detektor Fase AC Non Kontak [Diuji]](https://electronics.jf-parede.pt/img/sensors-detectors/38/non-contact-ac-phase-detector-circuit.png)

![Bangun Sirkuit Konverter Buck Sederhana [Konverter Step Down]](https://electronics.jf-parede.pt/img/3-phase-power/D0/build-a-simple-buck-converter-circuit-step-down-converter-1.jpg)