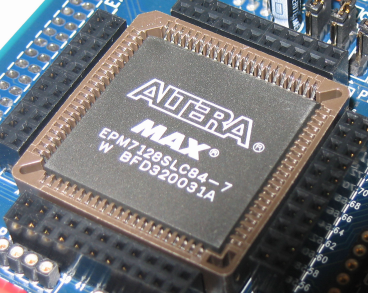

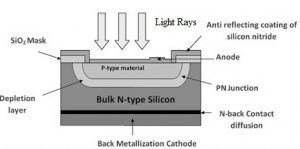

Istilah VLSI adalah singkatan dari 'Very Large Scale Integration Technology' yang melibatkan perancangan sirkuit terintegrasi (IC) dengan menggabungkan ribuan transistor logis ke dalam satu chip oleh sirkuit logika yang berbeda . IC ini akhirnya mengurangi ruang sirkuit yang ditempati jika dibandingkan dengan sirkuit dengan IC konvensional. Daya komputasi dan pemanfaatan ruang adalah tantangan utama desain VLSI. Menerapkan proyek VLSI membuka karir yang menantang dan cerah bagi mahasiswa serta peneliti. Beberapa area tren baru VLSI adalah Field Programmable Gate Array aplikasi (FPGA), desain ASIC, dan SOC. Daftar dari beberapa proyek VLSI diberikan di bawah ini untuk para siswa yang dengan sungguh-sungguh mencari proyek di bidang ini. Artikel ini membahas gambaran umum proyek VLSI berdasarkan FPGA, Xilinx, IEEE, Mini, Matlab, dll yang tercantum di bawah ini. Proyek-proyek ini sangat membantu mahasiswa teknik, mahasiswa M.tech.

Proyek VLSI untuk Mahasiswa Teknik

Proyek VLSI dengan abstrak untuk mahasiswa teknik elektronik dibahas di bawah ini.

Proyek VLSI

1). Transformasi Wavelet Diskrit berbasis 3D Lifting

Proyek ini membantu dalam menyediakan gambar yang sangat presisi dengan menggunakan pengkodean gambar tanpa kehilangan datanya. Untuk mencapai hal ini, proses ini mengimplementasikan filter pengangkatan tergantung pada transformasi arsitektur VLSI wavelet diskrit 3D.

2). Perancangan Pengganda SFQ dengan 4-bit dengan Efisien melalui Perangkat Keras Berkecepatan Tinggi

Proyek ini terutama digunakan untuk mengimplementasikan booth encoder (MBE) yang dimodifikasi dengan berbasis SFQ 4-bit pengali . Pengganda ini memberikan kinerja yang baik jika dibandingkan dengan pembuat enkode bilik konvensional. Proyek ini terutama digunakan dalam aplikasi penundaan kritis.

3). Prosesor Kriptografi yang digunakan dalam Kartu Cerdas dengan Area yang Efisien

Proyek ini digunakan untuk mengimplementasikan tiga algoritma kriptografi yang didukung oleh kunci privat & publik yang digunakan dalam kartu pintar aplikasi untuk menyediakan verifikasi & data pengguna yang sangat aman komunikasi .

4). Pengganda Berkecepatan Tinggi atau Berdaya Rendah dengan Metode Supresi Daya Palsu

Sistem yang diusulkan ini menyaring sinyal palsu yang tidak berguna dari unit aritmatika untuk menghindari transmisi data yang tidak perlu yang tidak mempengaruhi hasil komputasi terakhir. Sistem ini menggunakan metode SPST untuk pengganda untuk mencapai daya rendah dan transmisi data berkecepatan tinggi.

5). Kompresi & Dekompresi dari Algoritma Data Lossless

Proyek ini terutama diimplementasikan untuk arsitektur perangkat keras 2-tahap tergantung pada fitur algoritma PDLZW (Parallel Dictionary LZW) serta algoritma tipe Adaptive Huffman yang digunakan untuk aplikasi kompresi data lossless & dekompresi lossless.

6). Arsitektur Turbo Decoder dengan Kompleksitas Rendah untuk WSN Hemat Energi

Sistem yang diusulkan digunakan untuk mengurangi konsumsi energi total selama transmisi data WSN melalui algoritma penguraian LUT-Log-BCJR ke operasi ACS dasar (Tambah Bandingkan Pilihan).

7). Arsitektur VLSI untuk Menghapus Kebisingan Impuls dari Gambar dengan Efisien

Sistem yang diusulkan ini terutama digunakan untuk meningkatkan kualitas gambar secara visual untuk menghindari kemungkinan rusak dengan noise impuls untuk menerapkan arsitektur VLSI yang efisien dengan bantuan filter edge-preserving.

8). Arsitektur In-Memory-Processor yang digunakan untuk Kompresi Multimedia

Sistem yang diusulkan ini menyediakan arsitektur dengan kompleksitas rendah untuk a prosesor dalam memori untuk mendukung aplikasi multimedia seperti kompresi gambar, video melalui penerapan instruksi tunggal yang sangat besar, konsep data ganda & kata instruksi.

9). Teknik Sinkronisasi Waktu dengan Laju Simbol untuk Sistem OFDM Nirkabel dengan Daya Rendah

Sistem yang diusulkan ini terutama digunakan untuk meningkatkan tindakan OFDM nirkabel (Divisi Frekuensi Ortogonal Multiplexing ) melalui penurunan daya seluruh baseband dengan bantuan jam generator dengan pengontrol waktu sampel merdu fase & dinamis.

10). Implementasi Low Power & High-Speed Multiplier berbasis akumulator dengan SPST Adder & Verilog

Proyek ini digunakan untuk merancang daya rendah & MAC berkecepatan tinggi (pengganda dan akumulator) dengan menerima metode penindasan palsu dari daya pada MBE (enkoder stan yang dimodifikasi). Dengan menggunakan desain ini, disipasi daya seluruh switching dapat dihindari.

11). Desain & Implementasi Prosesor Robot dengan Mengaktifkan Anti-tabrakan dengan Teknologi RFID

Sistem yang diusulkan terutama digunakan untuk mengimplementasikan prosesor robot dengan anti-tabrakan untuk menghindari tabrakan fisik robot di lingkungan multi-robot. Algoritma ini terutama diimplementasikan menggunakan teknologi VHDL & RFID.

12). Perancangan Rangkaian Logika dengan Hemat Daya menggunakan Metode Adiabatic

Sistem ini mendemonstrasikan desain rangkaian logika secara efisien dengan metode adiabatik jika dibandingkan melalui desain CMOS konvensional dengan bantuan rangkaian yang menggunakan Gerbang NAND & NOR . Dengan menggunakan metode adiabatik, disipasi daya dalam jaringan dapat dikurangi serta mendaur ulang energi yang tersimpan dalam kapasitor beban.

3). Sistem Enkripsi untuk Meningkatkan Kecepatan Komputasi Sistem

Tujuan utama dari proyek ini adalah untuk meningkatkan keamanan transmisi data untuk meningkatkan kecepatan komputasi dengan mengimplementasikan algoritma AES menggunakan FPGA. Jadi, simulasi ini, serta desain matematis, dapat dilakukan dengan bantuan kode VHDL.

14). Blok IP AHM atau Bus Berkinerja Tinggi Tingkat Lanjut

Proyek ini terutama digunakan untuk merancang arsitektur Advanced Mikrokontroler Bus (AMB) dengan menggunakan AHBN (Advanced High-Performance Bus). Proyek ini dapat dirancang dengan kode VHDL dengan mengimplementasikan blok seperti master & save.

15). Multimode RF Transceiver berbasis DSM dengan Multichannel

Sistem ini terutama digunakan untuk merancang arsitektur pemancar & penerima multimode dan multisaluran RF dengan modulator Delta-Sigma. Sistem yang diusulkan ini menggunakan bahasa VHDL untuk mengimplementasikan dua arsitektur.

16). Konsentrator Knockout Switch menggunakan Asynchronous Transfer Mode

Dengan menggunakan proyek ini, sakelar knockout berdasarkan transfer asinkron dapat dirancang dengan bantuan alat seperti VHS & VHDL. Sakelar knock out ini dapat digunakan di jaringan paket sirkuit virtual serta aplikasi datagram.

17). Sintesis Perilaku Sirkuit Asinkron

Proyek ini terutama digunakan untuk menyediakan teknik sintesis perilaku yang digunakan untuk sirkuit asinkron. Kedua template seperti implementasi balsa & asynchronous adalah elemen utama dalam desain.

18). Desain AMBA menggunakan Compliant Memory Controller dari AHB

Proyek ini digunakan untuk merancang MC (pengontrol memori) bergantung pada AMBA (Advanced Microcontroller Bus Architecture) untuk pengontrolan memori sistem menggunakan memori utama seperti SRAM & ROM.

19). Menerapkan Implementasi Tree Adder

Carry tree adder berdasarkan desain VLSI disebut sebagai penambah kinerja terbaik dibandingkan dengan penambah biner biasa. Penambah yang diimplementasikan dalam proyek ini adalah spanning tree, kogge-stone, dan sparse kogge-stone.

20). Rotasi Sudut Tetap Berbasis Desain CORDIC

Konsep utama dari sistem yang diusulkan ini adalah memutar vektor menggunakan sudut tetap. Sudut ini diperlukan untuk game, robotika, pengolahan citra , dll. Dengan menggunakan proyek ini, rotasi vektor dapat dicapai dengan menggunakan sudut tertentu dengan desain CORDIC (komputer digital rotasi koordinat).

21). Desain Filter FIR dengan Aritmatika Terdistribusi dari Tabel Pencarian

Sistem yang diusulkan ini terutama meningkatkan Filter FIR kinerja dengan merancangnya menggunakan aritmatika terdistribusi dari tabel pencarian 3 dimensi sebagai pengganti pengali. Jadi desain ini dapat diimplementasikan menggunakan software seperti FPGA & Xilinx.

22). Dorong-Tarik Pulsed Latch dengan Kecepatan Tinggi & Kondisional Daya Rendah

Proyek ini digunakan untuk menjalankan pulsed latch yang hemat energi & berkinerja tinggi yang terutama digunakan untuk sistem VLSI dengan menggunakan topologi baru. Karena topologi ini terutama bergantung pada tahap akhir yang digerakkan dorong-tarik menggunakan dua jalur pemisah melalui generator pulsa bersyarat.

23). Arsitektur Aritmatika Coder VLSI di SPIHT

Sistem yang diusulkan ini meningkatkan throughput metode pengkodean aritmatika dalam kompresi gambar partisi himpunan dalam pohon hierarki (SPIHT) dengan arsitektur kecepatan tinggi yang bergantung pada FPGA.

24). Noise Suppression dari Sinyal EKG berdasarkan FPGA

Proyek ini digunakan untuk menahan noise dalam sinyal ECG melalui dua filter median dengan ukuran titik sampel 91 & 7 masing-masing. Jadi proses ini dapat dicapai melalui penerapan Desain FPGA berdasarkan kode VHDL.

25). Prosesor Skala Gambar Berkinerja Tinggi berbasis VLSI dengan Biaya Rendah

Proyek ini digunakan untuk mengimplementasikan algoritma untuk prosesor penskalaan gambar berdasarkan VLSI dengan lebih sedikit memori dan kinerja tinggi. Desain sistem yang diusulkan terutama berisi penggabungan filter, metode dinamis yang dapat dikonfigurasi ulang & berbagi perangkat keras untuk mengurangi biaya.

26). Desain & Implementasi Arsitektur Array Sistolik Secara Efisien

Konsep utama dari proyek ini adalah merancang model perangkat keras yang digunakan untuk pengali array sistolik. Array ini dapat digunakan terutama untuk menjalankan perkalian biner dengan bantuan platform VHDL. Perancangan sistem yang diusulkan dapat diimplementasikan dengan menggunakan software FPGA & Isim.

27). Desain & Sintesis QPSK menggunakan Kode VHDL

QPSK adalah salah satu metode modulasi utama. Metode ini digunakan dalam aplikasi radio satelit. Teknik modulasi ini dapat diterapkan melalui gerbang logika yang dapat dibalik. Perancangan teknik QPSK dapat dilakukan dengan bantuan kode VHDL.

28). Desain & Implementasi DDR SDRAM Controller dengan Kecepatan Tinggi

Sistem yang diusulkan digunakan untuk merancang pengontrol DDR SDRAM untuk mentransfer data burst tergantung pada kecepatan tinggi untuk menyinkronkan data ini di antara sirkuit sistem tertanam & DDR SDRAM. Dengan menggunakan bahasa VHDL, kode dapat dikembangkan.

29). Desain & Implementasi Prosesor RISC 32-bit

Konsep utama dari proyek ini adalah mengimplementasikan 32 bit RISC (Komputer Set Instruksi Berkurang) dengan bantuan alat seperti XILINK VIRTEX4. Dalam proyek ini, 16 set instruksi dirancang dimanapun setiap instruksi dapat dieksekusi dalam satu siklus CLK menggunakan metode pipelining lima fase.

30). Implementasi Bus Bridge antara AHB & OCP

Sistem yang diusulkan digunakan untuk merancang jembatan bus antara dua protokol yaitu umum & standar. Protokol komunikasi seperti AHB (Advanced High-performance Bus) & OCP (Open Core Protocol) sangat populer yang digunakan dalam aplikasi SoC (Sistem On-chip) .

Ide Proyek VLSI untuk Mahasiswa Teknik

Daftar proyek VLSI berdasarkan FPGA, MatLab, IEEE, dan Proyek Mini untuk mahasiswa teknik tercantum di bawah ini.

Proyek VLSI untuk Mahasiswa M. Tech

Daftar proyek VLSI berdasarkan Mahasiswa M. Tech meliputi berikut ini.

- Desain Sel Memori I0T berbasis RHBD & Sangat Dapat Diandalkan Area yang digunakan dalam Aplikasi Dirgantara

- Detektor Fase dengan Kecepatan Setengah Bertingkat digunakan untuk CLK & Sirkuit Pemulihan Data

- Komparator dengan Daya Rendah & Kecepatan Tinggi digunakan untuk Aplikasi Yang Tepat

- Gated Voltage Level Translator dengan Kinerja Tinggi & Multiplexer Terintegrasi

- Ternary Adder berbasis CNTFET dengan Kinerja Tinggi

- Desain Pembanding Besaran dengan Daya Rendah

- Desain Gerbang Logika Ambang Batas dengan Mode-Arus untuk Analisis Delay

- Desain Dekoder Garis Campuran-Logika dengan Daya Rendah & Kinerja Tinggi

- Desain Testabilitas Logika Konvensi Tidur

- Pengubah Level Tegangan untuk Aplikasi Pasokan Ganda dengan Kecepatan Tinggi & Hemat Daya

- Desain & Analisis Komparator Ekor Ganda Daya Rendah & Tegangan Rendah

- Desain Flip-Flop berdasarkan Pulse-Triggered dengan Daya Rendah menggunakan Metode Signal Feed-Through

- Desain Sirkuit Efisien berdasarkan Runtime Reconfigurable FETs

- Desain Pembanding Besaran dengan Daya Rendah

- Analisis Delay dari Desain Gerbang Logika dengan Ambang Mode Saat Ini

Itu Proyek VLSI berbasis FPGA untuk mahasiswa teknik dan Proyek mini desain CMOS VLSI tercantum di bawah ini.

- Desain & Karakterisasi Sirkuit Hardened SEU untuk FPGA berdasarkan SRAM

- Desain & Aplikasi Potensial CMOS hybrid berbasis Memristor Compact yang digunakan dalam FPGA

- Implementasi FPGA untuk Pengukuran Jarak Berbasis Sensor Ultrasonik

- Penerapan FPGA untuk Booth Multiplier dengan Spartan6 FPGA

- Transformasi Wavelet Diskrit berdasarkan Pengangkatan dengan Spartan3 FPGA

- Pengontrol ARM di Robotika menggunakan FPGA

- UART berbasis FPGA dengan Multichannel

- Meredam Kebisingan Sinyal EKG menggunakan FPGA

- Implementasi FPGA berbasis UTMI & Lapisan Protokol USB 2.0

- Implementasi Filter Median dengan Spartan3 FPGA

- Penerapan FPGA berbasis Algoritma AES

- Sistem Siaga Keamanan berbasis PIC untuk Penerapan FPGA dengan Spartan 3an

- Implementasi FPGA untuk Merancang Kontroler Sistem Penginderaan Jauh

- Kit Pengolahan Citra FPGA menggunakan Image Filtering Linear & Morfologi

- Penerapan Gambar Fusion Medis berbasis Spartan3 FPGA

Daftar Proyek mini VLSI menggunakan kode VHDL termasuk yang berikut ini.

- Pembanding dengan Kecepatan Tinggi menggunakan VLSI

- Pengganda Floating-Point menggunakan VLSI

- Konversi Binary to Grey berbasis VLSI

- Filter Digital

- CLK Gating berdasarkan VLSI

- Pengganda Weda

- CMOS FF menggunakan VLSI

- Arsitektur Parallel Processor menggunakan VLSI

- Full Adder berbasis VLSI

- Desain DRAM / Dynamic Random Access Memory berbasis VLSI

- SRAM Layout berdasarkan VLSI

- Prosesor Sinyal Digital berbasis VLSI

- Multiplexer berbasis VLSI

- Mendesain Unit MAC berdasarkan VLSI

- Diferensiator berbasis VLSI

- FFT berbasis VLSI atau Fast Fourier Transform

- Arsitektur Discrete Cosine Transform berdasarkan VLSI

- Desain Pengganda 16-bit menggunakan VLSI19

- Perancangan FIFO Buffer berbasis VLSI

- Akselerator Berkecepatan Tinggi berdasarkan VLSI

Proyek VLSI menggunakan MATLAB & Xilinx

Daftar proyek VLSI berdasarkan MATLAB dan Proyek VLSI menggunakan Xilinx meliputi berikut ini.

- Desain & Analisis Modem CDMA dengan MATLAB

- Desain Filter FIR menggunakan VHDL pada Analisis berbasis FPGA & MATLAB

- Simulasi Sistem untuk Teknik Otomotif berbasis ModelSim & Matlab atau Simulink

- Adders berbasis Xilinx seperti Ripple Carry & Carry Skip

- Unit Aritmatika berdasarkan Titik Mengambang 32-bit

- ALU berbasis Floating Point

- Prosesor RISC berbasis 32-bit

- Kemampuan Konvolusi Kode Ortogonal

- Mesin Penjual Otomatis berbasis Xilinx dan Verilog

- Penambah Awalan Paralel berbasis Xilinx dengan 256-bit

- Protokol untuk Otentikasi Reksa menggunakan Xilinx

- Struktur Akses dengan Siklus Tunggal untuk Uji Logika menggunakan Xilinx

- UTMI & Protocol Layer berbasis USB2.0 menggunakan Xilinx

- Konfigurasi Kompresi Data Dan Dekompresi menggunakan Xilinx FPGA

- FPGA berbasis BIST & Spartan Series berbasis Xilinx 4000

- Filter IIR berdasarkan MATLAB & VLSI

- Filter FIR menggunakan MATLAB

Proyek IEEE

Itu daftar Proyek IEEE VLSI tercantum di bawah ini.

- Sistem Otomasi Rumah Nirkabel berbasis VLSI menggunakan Bluetooth

- Menghapus Kebisingan Impuls dalam Gambar dengan menggunakan Arsitektur VLSI yang Efisien

- Arsitektur Prosesor-Dalam-Memori untuk Kompresi Multimedia

- Pemantauan Sistem Suhu menggunakan Cloud & IoT

- Implementasi Sistem OFDM dengan IFFT & FFT

- Desain & Implementasi Kode Hamming dengan Verilog

- Pengenalan Sidik Jari berbasis VHDL menggunakan Filter Gabor

- Pemetaan Ulang Fungsi Aritmatika dengan ROM Tergantung pada Pendekatan Pendekatan

- Analisis Efisiensi Tinggi & Kinerja Kepadatan Rendah Dekoder Kode Pemeriksaan Paritas dalam Aplikasi Daya Rendah

- Arsitektur FFT dengan Feedforward of Pipelined Radix-2k

- Desain Flip-Flop untuk Aplikasi VLSI menggunakan Teknologi CMOS dengan Kinerja Tinggi

- Desain Filter FIR dengan Tabel Pencarian oleh Aritmatika Terdistribusi

- VLSI berbasis Low Cost & Enhanced Image Scaling Processor

- Implementasi & Desain ASIC dari Advanced Turbo Encoder & Decoder dengan 3GPP LTE

- Dorong-Tarik Pulsed Latch dengan Daya Rendah & Kondisional Kecepatan Tinggi

- Pemindaian yang Ditingkatkan dalam Pengujian Pemindaian Daya Rendah

- Arsitektur Aritmatika Coder VLSI untuk SPIHT

- Penerapan VHDL untuk UART

- Regulator Tegangan berbasis VLSI dengan Drop Out Rendah

- Flash ADC Design dengan Enhanced Comparator Scheme

- Desain Pengganda Daya Rendah dengan Gaya Logika Penundaan Konstan Gabungan

- Pembanding Ekor Ganda dengan Kinerja Tinggi & Daya Rendah

- Sistem Penyimpanan Flash dengan Kinerja Tinggi tergantung pada Buffer Tulis & Memori Virtual

- FF Daya Rendah berdasarkan Pendekatan Stack Sleepy

- Pengoptimalan Daya LFSR untuk BIST Daya Rendah Diimplementasikan dalam HDL

- Desain & Implementasi Vending Machine dengan Verilog HDL

- Desain Akumulator Berdasarkan Pembangkitan Pola 3 Bobot dengan LP-LSFR

- Reed-Solomon Decoder dengan Kecepatan Tinggi & Kompleksitas Rendah

- Teknik Desain Pengganda Dadda Lebih Cepat

- Penerima Radio FM berbasis Demodulasi Digital

- Generasi Pola Tes dengan Skema BIST

- Implementasi Arsitektur VLSI dengan Pipa Berkecepatan Tinggi

- Desain Protokol OCP Bus On-Chip menggunakan Fungsi Bus

- Detektor Frekuensi Fase & Desain Pompa Pengisian digunakan untuk Loop Terkunci Fase Frekuensi Tinggi

- Desain Cache Memory & Cache Controller dengan VHDL

- Implementasi Kompresor Adder 3-2 & 4-2 Berbasis ASTRAN

- Sistem Penagihan Listrik Prabayar dengan Desain On-Chip

- Implementasi Tumpang tindih menggunakan sel Logika & Analisis Kekuatannya

- Carry Look Ahead Adder dengan Analisis Kinerja Bit Berbeda menggunakan VHDL

- Desain Lapisan Data Link dengan Wi-Fi MAC Protokol

- Implementasi FPGA untuk Mutual Authentication Protocol dengan Modular Arithmetic

- Pembangkitan Sinyal PWM menggunakan FPGA & Variable Duty Cycle

Proyek Waktu Nyata

Daftar Proyek VLSI real-time terutama mencakup proyek mini VLSI menggunakan kode VHDL dan proyek perangkat lunak VLSI untuk mahasiswa teknik ECE.

- Integrasi Pragmatis SRAM Row Cache dalam Arsitektur DRAM 3-D Heterogen Menggunakan TSV

- Teknik Uji Mandiri Bawaan untuk Diagnosis Kesalahan Penundaan dalam Array Gerbang yang Dapat Diprogram Lapangan Berbasis Cluster

- Desain ASIC dari Pengganda Kompleks

- Penerapan VLSI Berbiaya Rendah untuk Penghapusan Kebisingan Impuls yang Efisien

- Berbasis FPGA Ruang Vektor PWM IC Kontrol Untuk Penggerak Motor Induksi Tiga Fasa

- Implementasi VLSI Auto Correlator dan CORDIC Algorithm untuk WLAN Berbasis OFDM

- Ekstraksi Jalan Otomatis Menggunakan Citra Satelit Resolusi Tinggi

- Desain VHDL untuk Segmentasi Gambar Menggunakan Filter Gabor untuk Deteksi Penyakit

- Arsitektur Dekoder Turbo Kompleksitas Rendah untuk Jaringan Sensor Nirkabel yang Hemat Energi

- Peningkatan Kemampuan Konvolusi Kode Orthogonal Menggunakan Implementasi FPGA

- Desain dan Implementasi ALU Floating Point

- Desain CORDIC untuk Sudut Rotasi Tetap

- Kode Reed-Solomon Produk untuk Menerapkan NAND Flash Controller pada FPGA Chip

- Statistik Peningkatan Hasil Akses Baca SRAM Menggunakan Sirkuit Kapasitansi Negatif

- Manajemen Daya Antarmuka Jaringan MIMO pada Sistem Seluler

- Desain Standar Enkripsi Data untuk Enkripsi Data

- Daya Rendah dan Area Bawa Pilih Adder yang Efisien

- Sintesis dan Implementasi UART Menggunakan Kode VHDL

- Arsitektur yang Ditingkatkan untuk Unit Penambahan Titik Mengambang yang Terpadu

- Pemancar Semua Digital 1-Bit Berbasis FPGA yang Menggunakan Modulasi Delta-Sigma dengan Output RF untuk SDR

- Mengoptimalkan Penggunaan Pencarian Rantai di Dekoder BCH untuk Transmisi Tingkat Kesalahan Tinggi

- Desain Digital Transmitter DS-CDMA Menggunakan Verilog HDL dan FPGA

- Desain dan Implementasi Arsitektur Array Sistolik yang Efisien

- Algoritma Pembelajaran Dinamika Robot Berbasis VLSI

- Desain Unit Fungsional Multimedia Serbaguna Menggunakan Teknik Power Suppression Palsu

- Perancangan Jembatan Bus antara AHB dan OCP

- Sintesis Perilaku Sirkuit Asinkron

- Optimasi Kecepatan Decoder Viterbi Modifikasi Berbasis FPGA

- Implementasi Antarmuka I2C

- Pengganda Berkecepatan Tinggi / Berdaya Rendah Menggunakan Teknik Power Suppression Canggih

- Menjepit Tegangan Suplai Virtual dari Sirkuit Gerbang Daya untuk Pengurangan Kebocoran Aktif dan Keandalan Gerbang Oksida

- Penyalur Hemat Daya Berbasis FPGA untuk Radio yang Ditentukan Perangkat Lunak

- Arsitektur VLSI dan Pembuatan Prototipe FPGA dari Kamera Digital untuk Keamanan dan Otentikasi Gambar

- Peningkatan Operasi Robot Dalam Ruangan

- Perancangan dan Implementasi Jaringan Permutasi ON-Chip untuk Sistem Multiprosesor-On-Chip

- Metode Sinkronisasi Waktu Laju Simbol untuk Sistem OFDM Nirkabel Berdaya Rendah

- Kontroler DMA (Direct Memory Access) Menggunakan VHDL / VLSI

- FFT yang Dapat Dikonfigurasi Ulang Menggunakan Arsitektur Berbasis CORDIC untuk Penerima MIMI-OFDM

- Teknik Power Suppression Palsu untuk Aplikasi Multimedia / DSP

- Efisiensi Kode BCH dalam Watermarking Gambar Digital

- Pengontrol SD-RAM Kecepatan Data Ganda

- Menerapkan Filter Gabor untuk Pengenalan Sidik Jari Menggunakan Verilog HDL

- Desain Redundan Skala Nanometer Praktis melalui Pustaka Sel Standar Sadar untuk Peningkatan Redundan melalui 1 Rasio Penyisipan

- Algoritma Kompresi dan Dekompresi Data Lossless dan Arsitektur Perangkat Keras nya

- Kerangka Kerja untuk Koreksi Kesalahan Lunak Multi-Bit

- Kompresi Data Uji Efisien Berbasis Viterbi

- Implementasi Blok FFT / IFFT untuk OFDM

- Kompresi Gambar Berbasis Wavelet dengan VLSI Progressive Coding

- Implementasi VLSI dari Pengganda Pipelined Sepenuhnya Arsitektur DCT / IDCT Kurang dari 2d untuk Jpeg

- Emulasi Kesalahan Berbasis FPGA dari Sirkuit Sekuensial Sinkron

Jadi, ini semua tentang daftar proyek VLSI untuk teknik, mahasiswa M.Tech yang membantu dalam memilih topik proyek tahun terakhir mereka. Setelah menghabiskan waktu berharga Anda saat membaca daftar ini, kami yakin Anda telah mendapatkan ide yang cukup baik untuk memilih topik proyek pilihan Anda dari daftar proyek VLSI, dan berharap Anda memiliki cukup kepercayaan diri untuk mengambil topik apa pun dari daftar. Untuk detail lebih lanjut dan bantuan dengan proyek ini, Anda dapat menulis kepada kami di bagian komentar yang diberikan di bawah ini. Ini pertanyaan untuk Anda, apa itu VHDL?

Kredit Foto

- Proyek VLSI oleh set-tech