JTAG (Joint Test Action Group) adalah standar IEEE 1149.1 mapan yang dikembangkan pada tahun 1980 untuk memecahkan masalah manufaktur yang terjadi dalam papan elektronik atau papan sirkuit tercetak . Teknologi ini digunakan untuk menyediakan akses pengujian yang cukup untuk setiap papan kompleks ketika akses pengujian menurun. Dengan demikian, teknologi pemindaian batas diluncurkan & standar JTAG atau Spesifikasi JTAG didirikan. Kompleksitas elektronik semakin meningkat dari hari ke hari, sehingga spesifikasi JTAG telah menjadi format pengujian yang diterima untuk menguji unit elektronik yang rumit & ringkas. Artikel ini membahas tentang JTAG protokol – bekerja dengan aplikasi.

Apa itu JTAG?

Nama yang diberikan untuk IEEE 1149.1 Standard Test Access Port serta Boundary-Scan Architecture dikenal sebagai JTAG (Joint Test Action Group). Arsitektur pemindaian batas ini sebagian besar digunakan di dalam komputer prosesor karena prosesor pertama dengan JTAG dirilis oleh Intel. Standar IEEE ini hanya mendefinisikan bagaimana sirkuit komputer diuji untuk memastikan apakah itu berfungsi dengan benar setelah prosedur pembuatan. Pada papan sirkuit, tes dilakukan untuk memeriksa sambungan solder.

Joint Test Action Group memberikan tampilan pin-out untuk penguji dengan setiap pad IC yang membantu dalam mengidentifikasi kesalahan apa pun di dalam papan sirkuit. Setelah protokol ini dihubungkan ke sebuah chip, ini dapat melampirkan probe ke chip dengan memungkinkan pengembang untuk mengontrol chip serta koneksinya dengan chip lain. Antarmuka dengan grup Aksi Uji Gabungan juga dapat digunakan oleh Pengembang untuk menyalin firmware ke memori non-volatil di perangkat elektronik.

Konfigurasi/Pin Keluar

Kelompok Aksi Uji Gabungan mencakup 20 pin di mana setiap pin dan fungsinya dibahas di bawah ini.

Pin1 (VTref): Ini adalah pin tegangan referensi target yang digunakan untuk menghubungkan ke catu daya utama target yang berkisar antara 1,5 hingga 5,0VDC.

Pin2 (Vsupply): Ini adalah tegangan suplai target yang digunakan untuk menghubungkan suplai tegangan utama target 1.5VDC – 5.0VDC.

Pin3 (nTRST): Ini adalah pin reset tes yang digunakan untuk mereset mesin status pengontrol TAP.

Pin (4, 6, 8, 10, 12, 14, 16, 18 & 20): Ini adalah pin GND yang umum.

Pin5 (TDI): Ini adalah Data Uji Di pin. Data ini digeser ke perangkat target. Pin ini harus ditarik ke atas pada kondisi yang ditentukan di papan target.

Pin7 (TMS): Ini adalah pin Test Mode State yang ditarik untuk menentukan kondisi state machine kontroler TAP selanjutnya.

Pin9 (TCK): Ini adalah pin jam uji yang menyinkronkan operasi mesin keadaan internal di pengontrol TAP.

Pin11 (RTCK): Ini adalah pin TCK Pengembalian Input yang digunakan pada perangkat yang mendukung pencatatan jam kerja adaptif.

Pin13 (TDO): Ini adalah pin Test Data Out, jadi data dipindahkan dari perangkat target ke Flyswatter.

Pin15 (nSRST): Ini adalah pin Reset Sistem Target yang terhubung ke sinyal reset utama target.

Pin 17 & 19 (NC): Ini bukan pin yang terhubung.

Bekerja di JTAG

Penggunaan asli JTAG adalah untuk pengujian batas. Di sini, adalah papan sirkuit cetak sederhana termasuk dua IC seperti CPU & FPGA . Papan tipikal dapat mencakup banyak IC. Secara umum, IC mencakup banyak pin yang terhubung bersama dengan banyak koneksi. Di sini, dalam diagram berikut, hanya empat koneksi yang ditampilkan.

Jadi jika Anda mendesain banyak papan di mana setiap papan memiliki ribuan koneksi. Di dalamnya, ada beberapa papan yang buruk. Jadi kita perlu memeriksa papan mana yang berfungsi dan mana yang tidak berfungsi. Untuk itu, Kelompok Aksi Uji Gabungan dirancang.

Protokol ini dapat menggunakan pin kontrol dari semua chip tetapi dalam diagram berikut, Kelompok Aksi Uji Gabungan akan membuat semua pin output CPU & semua pin input FPGA. Setelah itu, dengan mengirimkan sejumlah data dari pin CPU & membaca nilai pin dari FPGA, JTAG menyatakan bahwa koneksi papan PCB baik-baik saja.

Sebenarnya, Kelompok Aksi Uji Gabungan mencakup empat sinyal logika TDI, TDO, TMS & TCK. Dan sinyal-sinyal ini perlu dihubungkan dengan cara tertentu. Pada awalnya, TMS & TCK terhubung secara paralel ke semua IC JTAG.

Setelah itu, baik TDI & TDO terhubung untuk membentuk rantai. Seperti yang dapat Anda amati, setiap IC yang sesuai dengan JTAG mencakup 4-pin yang digunakan untuk JTAG di mana 3-pin adalah input dan pin ke-4 adalah output. Pin kelima seperti TRST adalah opsional. Biasanya, pin JTAG tidak dibagikan untuk tujuan lain.

Dengan menggunakan Kelompok Aksi Uji Gabungan, semua IC menggunakan pengujian batas yang alasan aslinya dibuat oleh JTAG. Saat ini, penggunaan protokol ini telah diperluas untuk memungkinkan berbagai hal seperti mengkonfigurasi FPGA & setelah itu JTAG digunakan dalam inti FPGA untuk tujuan debugging.

Arsitektur JTAG

Arsitektur JTAG ditunjukkan di bawah ini. Dalam arsitektur ini, semua sinyal di antara logika inti perangkat & pin diinterupsi melalui jalur pemindaian serial yang disebut BSR atau Boundary Scan Register. BSR ini mencakup berbagai 'sel' pemindaian batas. Umumnya, sel pemindaian batas ini tidak terlihat tetapi dapat digunakan untuk mengatur atau membaca nilai dalam mode uji dari pin perangkat.

Antarmuka JTAG yang disebut TAP atau Test Access Port menggunakan sinyal yang berbeda untuk mendukung operasi pemindaian batas seperti TCK, TMS, TDI, TDO, dan TRST.

- Sinyal TCK atau Test Clock hanya menyinkronkan operasi di dalam mesin keadaan.

- Sinyal TMS atau Test Mode Select diambil sampelnya pada tepi yang meningkat dari sinyal jam uji untuk menentukan status berikutnya.

- Sinyal TDI atau Test Data In menandakan data yang digeser ke dalam perangkat uji atau logika pemrograman. Setelah mesin keadaan dalam berada dalam keadaan yang benar, maka itu diambil sampelnya di tepi TCK yang meningkat.

- Sinyal TDO atau Test Data Out menandakan data yang digeser keluar dari perangkat uji atau logika pemrograman. Setelah mesin keadaan dalam berada dalam keadaan yang benar maka itu berlaku di tepi menurun TCK

- TRST atau Test Reset adalah pin opsional yang digunakan untuk mereset state machine dari TAP controller.

Pengontrol TAP

Jalur akses uji dalam arsitektur JTAG terdiri dari pengontrol TAP, register instruksi & register data uji. Kontroler ini termasuk mesin status pengujian yang bertanggung jawab untuk membaca sinyal TMS & TCK. Di sini, pin i/p data hanya digunakan untuk memuat data ke dalam sel batas di antara inti IC & pin fisik, dan juga memuat data ke salah satu register data atau ke register instruksi. Data o/p pin digunakan untuk membaca data dari register atau sel batas.

Mesin status pengontrol TAP dikendalikan oleh TMS dan di-clock oleh TCK. State machine menggunakan dua jalur untuk menandakan dua mode berbeda seperti mode instruksi & mode data.

Daftar

Ada dua jenis register yang tersedia dalam pemindaian batas. Setiap perangkat yang sesuai mencakup minimal dua atau lebih register data & satu register instruksi.

Daftar Instruksi

Register instruksi digunakan untuk menyimpan instruksi saat ini. Jadi datanya digunakan oleh pengontrol TAP untuk memutuskan apa yang akan dieksekusi dengan sinyal yang diperoleh. Paling sering, data register instruksi akan menjelaskan sinyal register data mana yang harus dilewatkan.

Daftar Data

Register data tersedia dalam tiga jenis register BSR (Boundary Scan Register), BYPASS & ID CODE. Dan juga, register data lain mungkin ada, namun tidak diperlukan sebagai elemen standar JTAG.

Register Pemindaian Batas (BSR)

BSR adalah register data pengujian utama yang digunakan untuk memindahkan data dari dan ke pin I/O perangkat.

JALAN PINTAS

Bypass adalah register bit tunggal yang digunakan untuk melewatkan data dari TDI – TDO. Jadi memungkinkan perangkat tambahan dalam sirkuit untuk diuji dengan overhead minimum.

KODE ID

Jenis register data ini mencakup kode ID serta nomor revisi untuk perangkat. Jadi data ini memungkinkan perangkat terhubung ke file BSDL (Boundary Scan Description Language). File ini menyertakan detail konfigurasi Pemindaian Batas untuk perangkat.

Cara kerja JTAG adalah, pada awalnya, mode instruksi dipilih di mana salah satu keadaan dalam mode ini 'jalur' memungkinkan jam operator dalam instruksi oleh TDI. Setelah itu., mesin negara berkembang hingga diatur ulang. Langkah selanjutnya untuk sebagian besar instruksi adalah memilih mode data. Jadi dalam mode ini, data dimuat melalui TDI untuk dibaca dari TDO. Untuk TDI & TDO, jalur data akan diatur sesuai dengan instruksi yang telah di-clock. Setelah operasi baca/tulis selesai, mesin keadaan berkembang lagi ke keadaan reset.

Perbedaan antara JTAG Vs UART

Perbedaan antara JTAG dan UART adalah sebagai berikut.

| JTAG |

UART |

| Istilah “JTAG” adalah singkatan dari Joint Test Action Group. | Syarat ' UART ” adalah singkatan dari Universal Asynchronous Receiver/Transmitter. |

| Ini adalah antarmuka sinkron yang menggunakan perangkat keras bawaan untuk memprogram flash . | UART adalah antarmuka asinkron yang menggunakan bootloader yang berjalan di dalam memori. |

| Ini adalah satu set port uji yang digunakan untuk debugging tetapi juga dapat digunakan untuk memprogram firmware (yang biasa dilakukan).

|

UART adalah jenis chip yang mengontrol komunikasi ke dan dari perangkat, seperti mikrokontroler, ROM, RAM, dll. Sebagian besar waktu, itu adalah koneksi serial yang memungkinkan kita untuk berkomunikasi dengan perangkat. |

| Ini tersedia dalam empat jenis TDI, TDO, TCK, TMS & TRST. | Ini tersedia dalam dua jenis dumb UART & FIFO UART. |

| Joint Test Action Group adalah pemrograman serial atau protokol akses data yang digunakan dalam antarmuka mikrokontroler & perangkat terkait. | UART adalah salah satu jenis chip atau sub-komponen mikrokontroler yang digunakan untuk menyediakan perangkat keras untuk menghasilkan aliran serial asinkron seperti RS-232/RS-485. |

| Komponen JTAG adalah Prosesor, FPGA, CPLD , dll. | Komponen UART adalah generator CLK, register geser I/O, buffer pengirim atau penerima, buffer bus data sistem, logika kontrol baca atau tulis, dll. |

Penganalisis Protokol JTAG

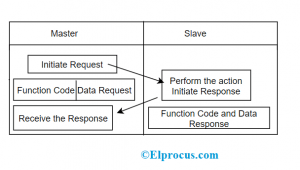

JTAG Protocol Analyzer seperti PGY-JTAG-EX-PD adalah salah satu jenis Protocol Analyzer termasuk beberapa fitur untuk menangkap & men-debug komunikasi di antara host & desain yang sedang diuji. Jenis penganalisis ini adalah instrumen terkemuka yang memungkinkan insinyur pengujian & desain untuk menguji desain tertentu JTAG untuk spesifikasinya melalui pengaturan PGY-JTAG-EX-PD seperti Master atau Slave untuk menghasilkan lalu lintas JTAG & mendekode paket dekode dari Protokol Kelompok Aksi Uji Gabungan.

Fitur

Fitur penganalisis protokol JTAG meliputi yang berikut ini.

- Mendukung hingga 25MH frekuensi JTAG.

- Ini menghasilkan lalu lintas JTAG & dekode protokol untuk Bus secara bersamaan.

- Ini memiliki Kemampuan Master JTAG.

- Variabel JTAG Kecepatan data & Siklus tugas.

- Penundaan TDI & TCK yang ditentukan pengguna.

- Komputer host antarmuka USB 2.0 atau 3.0.

- Analisis Kesalahan dalam Protokol Decode

- Diagram waktu bus yang didekodekan protokol.

- Streaming data protokol berkelanjutan ke komputer host untuk menyediakan buffer yang besar.

- Daftar aktivitas protokol.

- Pada berbagai kecepatan, skrip latihan dapat ditulis untuk menggabungkan beberapa generasi bingkai data.

Diagram Waktu

Itu diagram waktu dari JTAG protokol ditunjukkan di bawah ini. Dalam diagram berikut, pin TDO tetap dalam kondisi impedansi tinggi kecuali selama keadaan pengontrol shift-IR/shift-DR.

Pada kondisi kontroler shift-IR & Shift-DR, pin TDO diupdate pada sisi penurunan TCK melalui Target dan disampel pada sisi peningkatan TCK melalui Host.

Baik pin TDI & TMS hanya diambil sampelnya di tepi TCK yang meningkat melalui Target. Diperbarui di tepi yang menurun jika tidak TCK melalui Host.

Aplikasi

Itu aplikasi JTAG termasuk berikut ini.

- Kelompok Aksi Uji Gabungan sering digunakan dalam Prosesor untuk memberikan hak masuk ke fungsi emulasi atau debugnya.

- Semua CPLD & FPGA menggunakan ini sebagai antarmuka untuk memberikan akses ke fungsi pemrograman mereka.

- Ini digunakan untuk pengujian PCB tanpa akses fisik

- Ini digunakan untuk tes manufaktur tingkat papan.

Jadi, ini semua tentang gambaran umum tentang JTAG – konfigurasi pin, bekerja dengan aplikasi. JTAG standar industri digunakan untuk verifikasi desain serta pengujian PCB setelah pembuatan. Berikut adalah pertanyaan untuk Anda, JTAG singkatan?