Itu transistor efek medan (FET) adalah perangkat elektronik di mana sebuah Medan listrik digunakan untuk mengatur aliran arus. Untuk menerapkan ini, perbedaan potensial diterapkan di seluruh gerbang dan terminal sumber perangkat, yang mengubah konduktivitas antara saluran pembuangan dan terminal sumber yang menyebabkan arus terkontrol mengalir melintasi terminal ini.

FET dipanggil transistor unipolar karena ini dirancang untuk beroperasi sebagai perangkat jenis operator tunggal. Anda akan menemukan berbagai jenis transistor efek medan yang tersedia.

Simbol

Simbol grafis untuk JFET n-channel dan p-channel dapat divisualisasikan dalam gambar berikut.

Anda dapat dengan jelas memperhatikan bahwa tanda panah yang menunjuk ke dalam untuk perangkat saluran-n untuk menunjukkan arah di mana IG(arus gerbang) seharusnya mengalir ketika persimpangan p-n bias maju.

Dalam kasus perangkat saluran-p kondisinya identik kecuali perbedaan arah simbol panah.

Perbedaan antara FET dan BJT

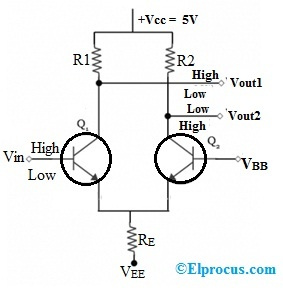

Transistor efek medan (FET) adalah perangkat tiga terminal yang dirancang untuk berbagai aplikasi rangkaian yang melengkapi, ke tingkat yang lebih tinggi, aplikasi transistor BJT.

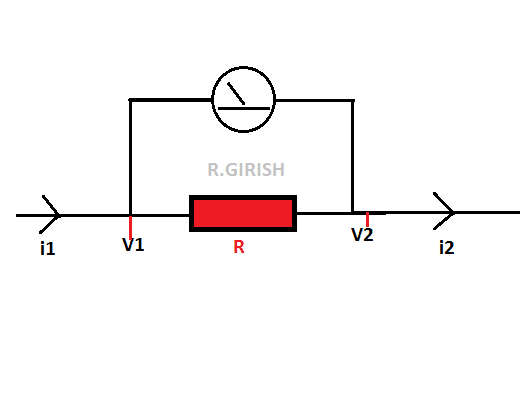

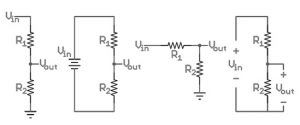

Meskipun Anda akan menemukan perbedaan yang signifikan antara BJT dan JFET, sebenarnya ada beberapa karakteristik yang cocok yang akan dibicarakan dalam diskusi berikut. Perbedaan utama antara perangkat ini adalah BJT adalah perangkat yang dikontrol arus seperti yang ditunjukkan pada Gambar 5.1a, sedangkan transistor JFET adalah perangkat yang dikontrol tegangan seperti yang ditunjukkan pada Gambar 5.1b.

Sederhananya, saya saat iniCpada Gambar 5.1a adalah fungsi langsung dari tingkat IB. Untuk FET, arus I adalah fungsi dari tegangan V.GSdiberikan ke sirkuit input seperti yang ditunjukkan pada Gambar. 5.1b.

Dalam kedua contoh, arus dari rangkaian keluaran akan diatur oleh parameter rangkaian masukan. Dalam satu situasi level arus dan dalam situasi lain tegangan yang diterapkan.

Sama seperti npn dan pnp untuk transistor bipolar, Anda akan menemukan transistor efek medan n-channel dan p-channel. Tetapi, Anda harus ingat bahwa transistor BJT adalah perangkat bipolar dengan awalan bi- menunjukkan bahwa tingkat konduksi adalah fungsi dari dua pembawa muatan, elektron dan lubang.

FET di sisi lain adalah perangkat unipolar yang hanya bergantung pada konduksi elektron (saluran-n) atau lubang (saluran-p).

Ungkapan 'efek medan' dapat dijelaskan seperti ini: kita semua mengetahui kekuatan magnet permanen untuk menarik serbuk logam ke arah magnet tanpa kontak fisik. Dengan cara yang sama di dalam FET, medan listrik dibuat oleh muatan yang ada yang mempengaruhi jalur konduksi dari rangkaian keluaran tanpa memiliki kontak langsung antara besaran yang dikendalikan dan yang dikendalikan. Mungkin salah satu fitur paling penting dari FET adalah impedansi masukannya yang tinggi.

Mulai dari besaran 1 hingga ratusan megohms, ia secara signifikan melampaui rentang resistansi masukan normal dari konfigurasi BJT, atribut yang sangat penting saat mengembangkan model penguat ac linier.

Namun, BJT memiliki sensitivitas yang lebih besar terhadap variasi sinyal input. Artinya, perubahan arus keluaran umumnya secara signifikan lebih banyak untuk BJT daripada FET untuk jumlah perubahan tegangan masukan yang sama.

Karena itu, penguatan tegangan ac standar untuk amplifier BJT bisa jauh lebih tinggi dibandingkan dengan FET.

Secara umum, FET jauh lebih tahan panas daripada BJT, dan juga seringkali berukuran lebih kecil dalam struktur dibandingkan dengan BJT, yang membuatnya secara khusus cocok untuk disematkan sebagai sirkuit terintegrasi (IC)keripik.

Karakteristik struktural dari beberapa FET, di sisi lain, dapat memungkinkan mereka menjadi sangat sensitif terhadap kontak fisik daripada BJT.

Lebih Banyak Hubungan BJT / JFET

- Untuk BJT VMENJADI= 0,7 V adalah faktor penting untuk memulai analisis konfigurasinya.

- Begitu pula dengan parameter IG= 0 A biasanya adalah hal pertama yang dipertimbangkan untuk analisis rangkaian JFET.

- Untuk konfigurasi BJT, IBsering kali merupakan faktor pertama yang perlu ditentukan.

- Demikian juga, untuk JFET, biasanya VGS.

Pada artikel kali ini kita akan fokus pada transistor JFET atau junction field effect, pada artikel selanjutnya kita akan membahas tentang transistor field-effcet metal-oksida-semikonduktor atau MOS-FET.

KONSTRUKSI DAN KARAKTERISTIK JFET

Seperti yang kita pelajari sebelumnya, JFET memiliki 3 prospek. Salah satunya mengontrol aliran arus antara dua lainnya.

Sama seperti BJT, di JFET juga perangkat n-channel digunakan lebih menonjol daripada rekan p-channel, karena perangkat n cenderung lebih efisien dan ramah pengguna dibandingkan dengan p-device.

Pada gambar berikut kita dapat melihat struktur dasar atau konstruksi JFET n-channel. Kita dapat melihat bahwa komposisi tipe-n membentuk saluran utama melintasi lapisan tipe-p.

Bagian atas saluran tipe-n dihubungkan melalui kontak Ohmic dengan terminal yang dinamai drain (D), sedangkan bagian bawah dari saluran yang sama juga dihubungkan melalui kontak Ohmic dengan terminal lain yang bernama sumber (S).

Sepasang material tipe-p dihubungkan bersama dengan terminal yang disebut sebagai gerbang (G). Pada dasarnya kami menemukan bahwa saluran pembuangan dan terminal sumber dihubungkan ke ujung saluran tipe-n. Terminal gerbang bergabung dengan sepasang material saluran-p.

Ketika tidak ada tegangan yang diterapkan melintasi jfet, dua persimpangan p-nnya tanpa kondisi bias. Dalam situasi ini terdapat daerah penipisan pada setiap persimpangan seperti yang ditunjukkan pada gambar di atas, yang terlihat seperti daerah dioda p-n tanpa bias.

Analogi Air

Operasi kerja dan kontrol JFET dapat dipahami melalui analogi air berikut.

Di sini, tekanan air dapat dibandingkan dengan besaran tegangan yang diberikan dari drain menuju sumber.

Aliran air dapat dibandingkan dengan aliran elektron. Mulut keran meniru terminal sumber JFET, sedangkan bagian atas keran tempat air dipaksa masuk menggambarkan Pembuangan JFET.

Kenop ketuk berfungsi seperti Gerbang JFET. Dengan bantuan potensi masukan, ia mengontrol aliran elektron (muatan) dari saluran ke sumber, seperti kenop keran mengontrol aliran air di lubang mulut.

Dari struktur JFET kita dapat melihat bahwa saluran pembuangan dan terminal sumber berada di ujung yang berlawanan dari saluran-n, dan sebagai istilah yang didasarkan pada aliran elektron kita dapat menulis:

V.GS= 0 V, VDSBeberapa Nilai Positif

Pada Gambar 5.4 kita dapat melihat tegangan positif VDSditerapkan di seluruh n-channel. Terminal gerbang langsung bergabung ke sumber untuk membuat kondisi VGS= 0V. Hal ini memungkinkan gerbang dan terminal sumber berada pada potensi yang identik, dan menghasilkan daerah penipisan ujung bawah dari setiap bahan-p, persis seperti yang kita lihat pada diagram pertama di atas dengan kondisi tanpa bias.

Begitu tegangan VDD(= VDS) diterapkan, elektron ditarik ke arah terminal pembuangan, menghasilkan aliran konvensional ID arus, seperti yang ditunjukkan pada Gambar 5.4.

Arah aliran muatan menunjukkan bahwa drain dan arus sumber sama besarnya (ID= SayaS). Sesuai dengan kondisi yang digambarkan pada Gambar 5.4, aliran muatan terlihat cukup tidak terbatas, dan hanya dipengaruhi oleh hambatan saluran-n antara saluran dan sumber.

Anda dapat mengamati bahwa daerah penipisan lebih besar di sekitar bagian atas kedua bahan tipe-p. Perbedaan ukuran wilayah ini idealnya dijelaskan melalui Gambar 5.5. Bayangkan memiliki resistansi seragam di saluran-n, ini bisa dibagi menjadi bagian-bagian yang ditunjukkan pada Gambar 5.5.

I saat iniDdapat membangun rentang tegangan melalui saluran seperti yang ditunjukkan pada gambar yang sama. Akibatnya daerah atas dari bahan tipe-p akan bias balik dengan tingkat sekitar 1,5 V, dengan daerah bawah hanya bias-balik sebesar 0,5 V.

Titik di mana persimpangan p-n bias-balik di sepanjang saluran menimbulkan arus gerbang dengan nol ampere seperti yang ditunjukkan pada gambar yang sama. Karakteristik inilah yang mengarah pada IG= 0 A adalah karakteristik penting dari JFET.

Sebagai VDSpotensi meningkat dari 0 menjadi beberapa volt, arus meningkat sesuai hukum Ohm dan plot IDbaris 5DSdapat terlihat seperti yang dibuktikan pada Gambar 5.6.

Ketelitian komparatif dari plotting menunjukkan bahwa untuk daerah-daerah bernilai rendah dari VDS, resistensi pada dasarnya seragam. Sebagai VDSnaik dan mendekati tingkat yang dikenal sebagai VP pada Gambar 5.6, daerah penipisan melebar seperti yang diberikan pada Gambar 5.4.

Hal ini menghasilkan penurunan lebar saluran yang nyata. Jalur konduksi yang menurun menyebabkan peningkatan resistansi sehingga menimbulkan kurva pada Gambar 5.6.

Semakin horizontal kurva, semakin tinggi resistansi, yang menunjukkan bahwa resistansi semakin menuju 'tak terbatas' ohm di wilayah horizontal. Saat VDSmeningkat ke tingkat di mana akan tampak bahwa dua daerah penipisan mungkin 'kontak' seperti yang ditunjukkan pada Gambar 5.7, menimbulkan situasi yang dikenal sebagai pinch-off.

Jumlah yang digunakan VDSmengembangkan situasi ini disebut menggentas tegangan dan itu dilambangkan dengan V.P.seperti yang disajikan pada Gambar 5.6. Secara umum, kata pinch-off menyesatkan karena mengandung makna I saat iniD'terjepit' dan jatuh ke 0 A. Seperti yang dibuktikan pada Gambar 5.6, hal ini hampir tidak terlihat jelas dalam kasus ini. sayaDmempertahankan tingkat saturasi yang dicirikan sebagai IDSSpada Gambar 5.6.

Yang benar adalah saluran yang sangat kecil terus ada, dengan arus konsentrasi yang sangat tinggi.

Titik di mana ID tidak hilang menggentas dan mempertahankan tingkat saturasi seperti yang ditunjukkan pada Gambar 5.6 dikonfirmasi dengan bukti berikut:

Karena tidak ada arus drain menghilangkan kemungkinan berbagai level potensial melalui material n-channel untuk menentukan jumlah perubahan bias balik di sepanjang persimpangan p-n. Hasil akhirnya adalah hilangnya distribusi wilayah penipisan yang dipicu menggentas memulai dengan.

Saat kami meningkatkan VDSdi atas VP., wilayah kontak dekat di mana dua wilayah penipisan akan bertemu satu sama lain bertambah panjang di sepanjang saluran. Namun level ID pada dasarnya tidak berubah.

Demikianlah momen VDSlebih tinggi dari V.p, JFET memperoleh karakteristik sumber arus.

Seperti yang dibuktikan pada Gambar 5.8, arus dalam JFET ditentukan di ID= SayaDSS, tetapi tegangan VDSlebih tinggi dari VP ditentukan oleh beban yang terhubung.

Pemilihan notasi IDSS didasarkan pada fakta bahwa itu adalah arus Drain to Source yang memiliki tautan hubung singkat melintasi gerbang ke sumber.

Penyelidikan lebih lanjut memberi kita evaluasi berikut:

sayaDSSadalah arus drain tertinggi untuk JFET dan ditentukan oleh kondisi VGS= 0 V dan VDS> | Wakil Presiden |.

Perhatikan bahwa pada Gambar 5.6 VGSadalah 0V untuk bentangan lengkap kurva. Pada bagian berikut kita akan mempelajari bagaimana atribut Gambar 5.6 menjadi dipengaruhi sebagai tingkat V.GSbervariasi.

V.GS <0V

Volatage yang diterapkan di seluruh gerbang dan sumber ditandai sebagai VGS, yang bertanggung jawab untuk mengendalikan operasi JFET.

Jika kita ambil contoh sebuah BJT, sama seperti kurva ICvs V.INIditentukan untuk berbagai level IB, Demikian pula kurva IDvs V.DSuntuk berbagai level VGSdapat dibuat untuk mitra JFET.

Untuk ini terminal gerbang ditetapkan pada potensi lanjutan yang lebih rendah di bawah tingkat potensi sumber.

Mengacu pada Gbr.5.9 di bawah ini, -1V diterapkan melintasi gerbang / terminal sumber untuk V tereduksiDStingkat.

Tujuan dari bias potensial negatif VGSadalah mengembangkan daerah penipisan menyerupai situasi V.GS= 0, tetapi pada V berkurang secara signifikanDS.

Hal ini menyebabkan gerbang mencapai titik jenuh dengan level V yang lebih rendahDSseperti yang ditunjukkan pada Gambar 5.10 (VGS= -1V).

Tingkat saturasi yang sesuai untuk IDdapat ditemukan berkurang dan sebenarnya terus menurun sebagai V.GSdibuat lebih negatif.

Anda dapat dengan jelas melihat pada Gambar 5.10 bagaimana tegangan pinch-off terus menurun dengan bentuk parabola sebagai VGSsemakin negatif.

Terakhir, saat VGS= -Vp, itu menjadi cukup negatif untuk menetapkan tingkat kejenuhan yang akhirnya 0 mA. Pada level ini, JFET sepenuhnya 'dimatikan'.

Tingkat VGSyang menyebabkan sayaDuntuk mencapai 0 mA ditandai dengan VGS= VP., dimana VP.adalah tegangan negatif untuk perangkat saluran-n dan tegangan positif untuk JFET saluran-p.

Biasanya, Anda mungkin menemukan sebagian besar lembar data JFET ditampilkan menggentas tegangan ditentukan sebagai V.GS (mati)bukannya VP..

Area di sisi kanan lokus pinch-off pada gambar di atas adalah tempat yang secara konvensional digunakan dalam amplifier linier untuk mendapatkan sinyal bebas distorsi. Wilayah ini biasa disebut arus konstan, saturasi atau wilayah amplifikasi linier.

Resistor yang dikontrol tegangan

Area yang berada di sisi kiri lokus pinch-off pada gambar yang sama disebut wilayah ohmik atau wilayah resistansi yang dikontrol tegangan.

Di wilayah ini, perangkat sebenarnya dapat dioperasikan sebagai resistor variabel (misalnya dalam aplikasi kontrol penguatan otomatis), dengan resistansi yang dikontrol melalui potensi gerbang / sumber yang diterapkan.

Anda dapat melihat bahwa kemiringan masing-masing kurva yang juga menandakan resistansi drain / sumber JFET untuk VDS

Saat kita membuat VGS lebih tinggi dengan potensi negatif, kemiringan setiap kurva menjadi semakin horizontal, menunjukkan tingkat resistensi yang meningkat secara proporsional.

Kami bisa mendapatkan pendekatan awal yang baik untuk tingkat resistansi sehubungan dengan tegangan VGS, melalui persamaan berikut.

p-Channel JFET Bekerja

Tata letak dan konstruksi internal JFET saluran-p persis sama dengan mitra saluran-n, kecuali bahwa daerah material jenis-p dan n dibalik, seperti yang ditunjukkan di bawah ini:

Arah aliran arus juga dapat dilihat sebagai terbalik, bersama dengan polaritas tegangan VGS dan VDS yang sebenarnya. Dalam kasus JFET p-channel, saluran akan dibatasi sebagai respons terhadap peningkatan potensi positif di seluruh gerbang / sumber.

Notasi dengan subskrip ganda untuk VDSakan menimbulkan tegangan negatif untuk VDS, seperti yang ditunjukkan pada karakteristik Gbr.5.12. Di sini, Anda dapat menemukan IDSSpada 6 mA, sedangkan tegangan pinch-off pada V.GS= + 6V.

Mohon jangan bingung karena ada tanda minus untuk VDS. Ini hanya menunjukkan bahwa sumber membawa potensi yang lebih tinggi daripada saluran pembuangan.

Anda dapat melihat bahwa kurva untuk V tinggiDSlevel tiba-tiba naik ke nilai yang terlihat tidak dibatasi. Kenaikan yang ditunjukkan secara vertikal melambangkan situasi kerusakan, yang berarti arus melalui perangkat saluran sepenuhnya dikendalikan oleh sirkuit eksternal pada titik waktu ini.

Meskipun hal ini tidak tampak pada Gbr.5.10 untuk perangkat saluran-n, ini mungkin terjadi di bawah tegangan yang cukup tinggi.

Wilayah ini bisa dihilangkan jika VDS (maks)dicatat dari lembar data perangkat, dan perangkat dikonfigurasi sedemikian rupa sehingga V yang sebenarnyaDSnilai lebih rendah dari nilai yang dicatat ini untuk setiap VGS.

Sepasang: 5 Sirkuit Amplifier 40 Watt Terbaik yang Dijelajahi Berikutnya: Lembar Data 2N3055, Pinout, Sirkuit Aplikasi