Ada suatu era, di mana komputer berukuran sangat besar sehingga untuk menginstalnya, dengan mudah dibutuhkan ruang ruangan. Tetapi hari ini mereka sangat berkembang sehingga kita bahkan dapat membawanya sebagai notebook dengan mudah. Inovasi yang memungkinkan hal ini adalah konsep Sirkuit Terpadu. Di Sirkuit terintegrasi , sejumlah besar aktif dan elemen pasif bersama dengan interkoneksi mereka dikembangkan melalui wafer silikon kecil biasanya berukuran 50 kali 50 mil dalam penampang. Proses dasar yang diikuti untuk produksi sirkuit tersebut meliputi pertumbuhan epitaxial, difusi pengotor bertopeng, pertumbuhan oksida, dan etsa oksida, menggunakan fotolitografi untuk membuat pola.

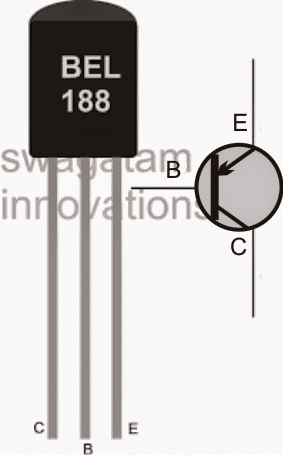

Komponen di atas wafer termasuk resistor, transistor, dioda, kapasitor, dll. Elemen yang paling rumit untuk diproduksi di atas IC adalah transistor. Transistor terdiri dari berbagai jenis seperti CMOS, BJT, FET. Kami memilih jenis teknologi transistor yang akan diterapkan di atas IC berdasarkan persyaratan. Pada artikel ini mari kita membiasakan diri dengan konsep Fabrikasi CMOS (atau) fabrikasi transistor sebagai CMOS.

Fabrikasi CMOS

Untuk kebutuhan disipasi daya yang lebih sedikit Teknologi CMOS digunakan untuk mengimplementasikan transistor. Jika kita membutuhkan rangkaian yang lebih cepat maka transistor diimplementasikan IC menggunakan BJT . Fabrikasi Transistor CMOS karena IC dapat dilakukan dalam tiga metode berbeda.

Teknologi sumur-N / sumur-P, di mana difusi tipe-n dilakukan pada substrat tipe-p atau difusi tipe-p dilakukan pada substrat tipe-n masing-masing.

Itu Teknologi sumur kembar , dimana NMOS dan transistor PMOS dikembangkan di atas wafer dengan difusi simultan di atas basis pertumbuhan epitaxial, bukan substrat.

Proses silikon On Insulator, di mana daripada menggunakan silikon sebagai substrat, bahan isolator digunakan untuk meningkatkan kecepatan dan kerentanan penguncian.

Teknologi N- well / P- well

CMOS dapat diperoleh dengan mengintegrasikan keduanya Transistor NMOS dan PMOS di atas wafer silikon yang sama. Dalam teknologi N-well, sumur tipe-n tersebar pada substrat tipe-p sedangkan pada sumur P-well sebaliknya.

Langkah Fabrikasi CMOS

Itu Proses fabrikasi CMOS mengalir dilakukan dengan menggunakan dua puluh langkah fabrikasi dasar saat diproduksi menggunakan teknologi N- well / P-well.

Pembuatan CMOS menggunakan N well

Langkah 1: Pertama kita memilih substrat sebagai dasar fabrikasi. Untuk N- well, substrat silikon tipe-P dipilih.

Substrat

Langkah 2 - Oksidasi: Difusi selektif dari pengotor tipe-n dilakukan dengan menggunakan SiO2 sebagai penghalang yang melindungi bagian dari wafer terhadap kontaminasi substrat. SiOduadilakukan dengan proses oksidasi yang dilakukan dengan mengekspos substrat ke oksigen dan hidrogen berkualitas tinggi dalam ruang oksidasi di sekitar 10000c

Oksidasi

Langkah 3 - Menumbuhkan Photoresist: Pada tahap ini untuk memungkinkan etsa selektif, lapisan SiO2 dikenakan proses fotolitografi. Dalam proses ini, wafer dilapisi dengan film seragam dari emulsi fotosensitif.

Berkembangnya Photoresist

Langkah 4 - Masking: Langkah ini merupakan kelanjutan dari proses fotolitografi. Pada langkah ini, pola keterbukaan yang diinginkan dibuat dengan menggunakan stensil. Stensil ini digunakan sebagai masker di atas fotoresis. Media sekarang terbuka sinar UV photoresist yang ada di bawah daerah topeng yang terbuka akan terpolimerisasi.

Masking dari Photoresist

Langkah 5 - Penghapusan Photoresist yang Tidak Terekspos: Topeng dilepas dan daerah fotoresis yang tidak terpapar dilarutkan dengan mengembangkan wafer menggunakan bahan kimia seperti Trichloroethylene.

Penghapusan Photoresist

Langkah 6 - Etsa: Wafer direndam dalam larutan etsa dari asam fluorida, yang menghilangkan oksida dari area di mana dopan akan menyebar.

Etsa SiO2

Langkah 7 - Penghapusan Seluruh Lapisan Photoresist: Selama proses etsa , bagian SiO2 yang dilindungi oleh lapisan fotoresis tidak terpengaruh. Topeng photoresist sekarang dilepas dengan pelarut kimia (H2SO4 panas).

Penghapusan Lapisan Photoresist

Langkah 8 - Pembentukan sumur-N: Pengotor tipe-n menyebar ke dalam substrat tipe-p melalui daerah yang terbuka sehingga membentuk sumur-N.

Pembentukan N-well

Langkah 9 - Penghapusan SiO2: Lapisan SiO2 sekarang dihilangkan dengan menggunakan asam fluorida.

Penghapusan SiO2

Langkah 10 - Deposisi Polysilicon: Ketidaksejajaran gerbang a Transistor CMOS akan menyebabkan kapasitansi yang tidak diinginkan yang dapat merusak rangkaian. Jadi untuk mencegah “proses gerbang selaras sendiri” ini lebih disukai di mana daerah gerbang terbentuk sebelum pembentukan sumber dan drain menggunakan implantasi ion.

Deposisi Polysilicon

Polysilicon digunakan untuk pembentukan pintu gerbang karena dapat menahan suhu tinggi lebih dari 80000c ketika wafer mengalami metode anil untuk pembentukan sumber dan tiriskan. Polysilicon disimpan dengan menggunakan Proses Deposisi Bahan Kimia di atas lapisan tipis oksida gerbang. Gerbang oksida tipis di bawah lapisan Polysilicon ini mencegah doping lebih lanjut di bawah wilayah gerbang.

Langkah 11 - Pembentukan Wilayah Gerbang: Kecuali dua daerah yang dibutuhkan untuk pembentukan gapura Transistor NMOS dan PMOS bagian Polysilicon yang tersisa dilucuti.

Pembentukan Wilayah Gerbang

Langkah 12 - Proses Oksidasi: Lapisan oksidasi diendapkan di atas wafer yang bertindak sebagai pelindung untuk selanjutnya proses difusi dan metalisasi .

Proses Oksidasi

Langkah 13 - Masking dan Difusi: Untuk membuat daerah untuk difusi pengotor tipe-n menggunakan proses masking dibuat celah kecil.

Masking

Menggunakan proses difusi tiga wilayah n + dikembangkan untuk pembentukan terminal NMOS.

Difusi-N

Langkah 14 - Penghapusan Oksida: Lapisan oksida dilepaskan.

Penghapusan Oksida

Langkah 15 - Difusi tipe-P: Mirip dengan difusi tipe-n untuk membentuk terminal difusi tipe-p PMOS dilakukan.

Difusi Tipe-P

Langkah 16 - Peletakan oksida medan tebal: Sebelum membentuk terminal logam, oksida medan tebal diletakkan untuk membentuk lapisan pelindung untuk daerah wafer di mana tidak diperlukan terminal.

Lapisan oksida medan tebal

Langkah 17 - Metalisasi: Langkah ini digunakan untuk pembentukan terminal logam yang dapat menyediakan interkoneksi. Alumunium tersebar di seluruh wafer.

Metalisasi

Langkah 18 - Penghapusan Kelebihan Logam: Logam berlebih dikeluarkan dari wafer.

Langkah 19 - Pembentukan Terminal: Di celah yang terbentuk setelah pemindahan terminal logam berlebih dibentuk untuk interkoneksi.

Pembentukan Terminal

Langkah 20 - Menetapkan Nama Terminal: Nama diberikan ke terminal Transistor NMOS dan PMOS .

Menetapkan nama Terminal

Pembuatan CMOS menggunakan Teknologi P well

Proses sumur-p mirip dengan proses sumur N kecuali di sini substrat tipe-n digunakan dan difusi tipe-p dilakukan. Untuk kesederhanaan biasanya, proses sumur N lebih disukai.

Fabrikasi Tabung Kembar CMOS

Dengan menggunakan proses Twin-tube, seseorang dapat mengontrol penguatan perangkat tipe P dan N. Berbagai langkah terlibat dalam pembuatan CMOS menggunakan metode Twin-tube adalah sebagai berikut

- Substrat tipe n atau p yang dikotori ringan diambil dan lapisan epitaxial digunakan. Lapisan epitaxial melindungi masalah penguncian di dalam chip.

- Lapisan silikon dengan kemurnian tinggi dengan ketebalan terukur dan konsentrasi dopan yang tepat dikembangkan.

- Pembentukan tabung untuk sumur P dan N.

- Konstruksi oksida tipis untuk perlindungan dari kontaminasi selama proses difusi.

- Sumber dan drainase dibentuk menggunakan metode implantasi ion.

- Pemotongan dilakukan untuk membuat bagian kontak logam.

- Metalisasi dilakukan untuk menggambar kontak logam

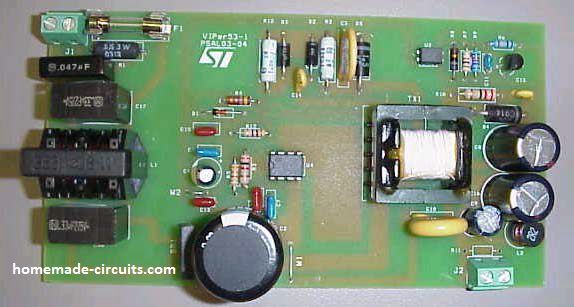

Tata Letak IC CMOS

Tampak atas ke CMOS fabrikasi dan tata letak diberikan. Di sini berbagai kontak logam dan difusi sumur N dapat dilihat dengan jelas.

Tata Letak IC CMOS

Jadi, ini semua tentang Teknik fabrikasi CMOS . Mari kita pertimbangkan wafer 1 dalam persegi dibagi menjadi 400 keping dengan luas permukaan 50 mil kali 50 mil. Dibutuhkan area seluas 50 mil2 untuk membuat transistor. Oleh karena itu setiap IC berisi 2 transistor sehingga terdapat 2 x 400 = 800 transistor yang dibangun pada setiap wafer. Jika 10 wafer diproses setiap batch maka 8000 transistor dapat diproduksi secara bersamaan. Apa sajakah komponen yang telah Anda amati pada sebuah IC?