Di sirkuit kombinasional, gerbang logika yang berbeda digunakan untuk mendesain encoder, multiplexer, decoder & de-multiplexer. Rangkaian ini memiliki beberapa karakteristik seperti keluaran dari rangkaian ini terutama tergantung pada level yang ada di terminal masukan setiap saat. Sirkuit ini tidak menyertakan memori apa pun. Keadaan awal masukan tidak memiliki pengaruh apa pun pada keadaan saat ini dari rangkaian ini. Input dan output dari rangkaian kombinasional adalah 'n' no. masukan & 'm' no. dari keluaran. Beberapa rangkaian kombinasional tersebut adalah half adder dan full adder, subtractor, encoder, decoder, multiplexer, dan demultiplexer. Artikel ini membahas ikhtisar tentang setengah penjumlahan dan penambah penuh dan berfungsi dengan tabel kebenaran.

Apa itu Adder?

Penambah adalah sirkuit logika digital dalam elektronik yang banyak digunakan untuk penambahan angka. Di banyak komputer dan jenis prosesor lainnya, penambah bahkan digunakan untuk menghitung alamat dan aktivitas terkait dan menghitung indeks tabel di ALU dan bahkan digunakan di bagian lain dari prosesor. Ini dapat dibangun untuk banyak representasi numerik seperti kelebihan-3 atau desimal berkode biner. Adders pada dasarnya diklasifikasikan menjadi dua jenis: Half Adder dan Full Adder.

Apa itu Sirkuit Half Adder dan Full Adder?

Sirkuit half adder memiliki dua input: A dan B, yang menambahkan dua digit input dan menghasilkan carry dan sum. Sirkuit penambah penuh memiliki tiga input: A dan C, yang menambahkan tiga angka input dan menghasilkan carry dan sum. Artikel ini memberikan informasi mendetail tentang apa tujuan half adder dan penambah penuh dalam bentuk tabel dan bahkan dalam diagram sirkuit juga. Telah disebutkan bahwa tujuan utama dan krusial dari penambah adalah penjumlahan. Berikut detailnya teori penambah setengah dan penambah penuh.

Basic Half Adder dan Full Adder

Half Adder

Jadi, datang ke skenario setengah penjumlah, ia menambahkan dua digit biner di mana bit input disebut sebagai augend dan addend dan hasilnya adalah dua keluaran, satu adalah penjumlahan dan yang lainnya adalah carry. Untuk melakukan operasi penjumlahan, XOR diterapkan ke kedua input, dan gerbang AND diterapkan ke kedua input untuk menghasilkan carry.

Diagram Fungsional HA

Sedangkan dalam rangkaian penambah penuh, ia menambahkan 3 angka satu-bit, di mana dua dari tiga bit dapat disebut sebagai operan dan yang lainnya disebut sebagai bit yang dibawa masuk. Output yang dihasilkan adalah output 2-bit dan ini dapat disebut sebagai output carry dan sum.

Dengan menggunakan setengah penjumlah, Anda dapat mendesain penambahan sederhana dengan bantuan gerbang logika.

Mari kita lihat contoh menambahkan dua bit tunggal.

2-bit tabel kebenaran setengah penambah adalah seperti di bawah ini:

Tabel Kebenaran Setengah Adder

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Ini adalah kombinasi bit tunggal yang paling mungkin. Tetapi hasil untuk 1 + 1 adalah 10, hasil penjumlahan harus ditulis ulang sebagai keluaran 2-bit. Dengan demikian, persamaan dapat ditulis sebagai

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Output '1' dari '10' adalah pelaksanaan. 'SUM' adalah keluaran normal dan 'CARRY' adalah pelaksanaannya.

Sekarang telah jelas bahwa penambah 1-bit dapat dengan mudah diimplementasikan dengan bantuan Gerbang XOR untuk keluaran 'SUM' dan Gerbang AND untuk 'Bawa'.

Misalnya, ketika kita perlu menambahkan, dua byte 8-bit bersama-sama, maka itu dapat diterapkan dengan menggunakan rangkaian logika penambah penuh. Setengah-penjumlah berguna saat Anda ingin menambahkan satu jumlah digit biner.

Cara untuk mengembangkan penjumlah dua digit biner adalah dengan membuat tabel kebenaran dan menguranginya. Saat Anda ingin membuat penjumlah tiga digit biner, operasi penjumlahan setengah penjumlahan dilakukan dua kali. Dengan cara yang sama, ketika Anda memutuskan untuk membuat penjumlah empat digit, operasi dilakukan sekali lagi. Dengan teori ini, jelas bahwa implementasinya sederhana, tetapi pengembangan adalah proses yang memakan waktu.

Ekspresi paling sederhana menggunakan fungsi OR eksklusif:

Jumlah = A XOR B

Bawa = A DAN B

Diagram Logis HA

Dan ekspresi yang setara dalam hal dasar AND, OR, dan NOT adalah:

SUM = A.B + A.B '

Kode VHDL Untuk Half Adder

Entitas ha adalah

Port (a: di STD_LOGIC

b: di STD_LOGIC

sha: keluar STD_LOGIC

cha: keluar STD_LOGIC)

akhir ha

Perilaku Arsitektur dari rangkaian di atas adalah

mulai

sha<= a xor b

tidak<= a and b

mengakhiri Perilaku

Nomor IC Setengah Adder

Penerapan half adder dapat dilakukan melalui sirkuit terintegrasi logika digital CMOS berkecepatan tinggi seperti seri 74HCxx yang mencakup SN74HC08 (7408) & SN74HC86 (7486).

Batasan Setengah Adder

Alasan utama untuk memanggil penambah biner ini seperti Penambah Setengah adalah, bahwa tidak ada rentang untuk menyertakan bit pembawa menggunakan bit sebelumnya. Jadi, ini adalah batasan utama HA yang pernah digunakan seperti penambah biner terutama dalam situasi waktu nyata yang melibatkan penambahan beberapa bit. Jadi keterbatasan ini bisa diatasi dengan menggunakan full adders.

Adder penuh

Penambah ini sulit diterapkan jika dibandingkan dengan penjumlahan setengah.

Diagram Fungsional Adder Lengkap

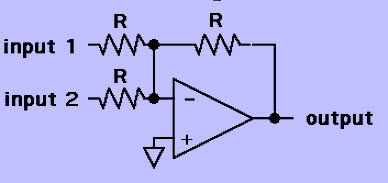

Perbedaan antara half-adder dan full-adder adalah full-adder memiliki tiga input dan dua output, sedangkan half adder hanya memiliki dua input dan dua output. Dua input pertama adalah A dan B dan input ketiga adalah input carry sebagai C-IN. Ketika logika full-adder dirancang, Anda merangkai delapan di antaranya untuk membuat adder selebar byte dan mengalirkan bit carry dari satu adder ke adder berikutnya.

Tabel Kebenaran FA

Output carry ditetapkan sebagai C-OUT dan output normal direpresentasikan sebagai S yaitu 'SUM'.

Dengan di atas tabel kebenaran penambah penuh , implementasi rangkaian penambah penuh dapat dipahami dengan mudah. SUM 'S' diproduksi dalam dua langkah:

- Dengan XORing input yang diberikan 'A' dan 'B'

- Hasil dari A XOR B kemudian di-XOR dengan C-IN

Ini menghasilkan SUM dan C-OUT benar hanya jika dua dari tiga input TINGGI, maka C-OUT akan TINGGI. Jadi, kita dapat menerapkan rangkaian penambah penuh dengan bantuan dua rangkaian penambah setengah. Awalnya, penjumlah setengah akan digunakan untuk menambahkan A dan B untuk menghasilkan Jumlah parsial dan logika penjumlah babak kedua dapat digunakan untuk menambahkan C-IN ke Jumlah yang dihasilkan oleh penjumlah babak pertama untuk mendapatkan keluaran S akhir.

Jika salah satu dari logika half adder menghasilkan carry, maka akan ada output carry. Jadi, C-OUT akan menjadi fungsi OR dari output Carry setengah penambah. Lihatlah implementasi rangkaian penambah penuh yang ditunjukkan di bawah ini.

Diagram Logika Adder Lengkap

Implementasi diagram logika yang lebih besar dimungkinkan dengan logika penambah penuh di atas, simbol yang lebih sederhana sebagian besar digunakan untuk mewakili operasi. Diberikan di bawah ini adalah representasi skematik yang lebih sederhana dari penambah penuh satu-bit.

Dengan jenis simbol ini, kita dapat menambahkan dua bit bersama-sama, mengambil carry dari urutan besaran yang lebih rendah berikutnya, dan mengirim carry ke urutan besaran berikutnya yang lebih tinggi. Di komputer, untuk operasi multi-bit, setiap bit harus diwakili oleh penambah penuh dan harus ditambahkan secara bersamaan. Jadi, untuk menambahkan dua bilangan 8-bit, Anda memerlukan 8 penjumlah penuh yang dapat dibentuk dengan mengalirkan dua dari blok 4-bit.

Half Adder dan Full Adder menggunakan K-Map

Bahkan output sum and carry untuk half adder juga bisa didapatkan dengan metode peta Karnaugh (K-map). Itu ekspresi boolean penambah setengah dan penambah penuh bisa didapatkan melalui K-map. Jadi, K-map untuk penambah ini dibahas di bawah.

K-map penambah setengah adalah

HA K-Map

Penambah lengkap K-Map adalah

FA K-Map

Ekspresi Logis dari SUM dan Carry

Ekspresi logis dari jumlah (S) dapat ditentukan berdasarkan input yang disebutkan dalam tabel.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ’+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

Ekspresi logis dari carry (Cout) dapat ditentukan berdasarkan input yang disebutkan dalam tabel.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

Dengan tabel kebenaran yang disebutkan di atas, maka dapat diperoleh hasil dan prosedurnya adalah:

Sirkuit kombinasional menggabungkan gerbang yang berbeda di sirkuit di mana itu bisa menjadi encoder, decoder, multiplexer dan demultiplexer . Karakteristik rangkaian kombinasional adalah sebagai berikut.

- Output pada setiap saat hanya didasarkan pada level yang ada di terminal input.

- Itu tidak menggunakan memori apa pun. Keadaan masukan sebelumnya tidak berpengaruh pada keadaan rangkaian saat ini.

- Ia dapat memiliki sejumlah input dan m jumlah output.

Pengkodean VHDL

Pengkodean VHDL untuk penambah penuh termasuk yang berikut ini.

entitas full_add adalah

Port (a: di STD_LOGIC

b: di STD_LOGIC

cin: di STD_LOGIC

jumlah: keluar STD_LOGIC

cout: keluar STD_LOGIC)

akhiri full_add

Perilaku Arsitektur full_add adalah

komponen ha adalah

Port (a: di STD_LOGIC

b: di STD_LOGIC

sha: keluar STD_LOGIC

cha: keluar STD_LOGIC)

komponen akhir

sinyal s_s, c1, c2: STD_LOGIC

mulai

HA1: peta pelabuhan ha (a, b, s_s, c1)

HA2: peta pelabuhan ha (s_s, cin, sum, c2)

biaya<=c1 or c2

mengakhiri Perilaku

Itu perbedaan antara half adder dan full adder adalah bahwa penambah setengah membuahkan hasil dan penambah penuh menggunakan penambah setengah untuk menghasilkan beberapa hasil lainnya. Demikian pula, jika Full-Adder terdiri dari dua Half-Adders, Full-Adder adalah blok aktual yang kita gunakan untuk membuat rangkaian aritmatika.

Bawa Lookahead Adders

Dalam konsep rangkaian penambah riak pembawa, bit yang diperlukan untuk penambahan segera tersedia. Padahal setiap bagian adder perlu menahan waktu kedatangan carry dari adder block sebelumnya. Karena itu, dibutuhkan lebih banyak waktu untuk menghasilkan SUM dan CARRY karena setiap bagian di sirkuit menunggu kedatangan input.

Misalnya, untuk mengirimkan keluaran untuk blok ke-n, ia perlu menerima masukan dari blok (n-1). Dan penundaan ini juga disebut sebagai penundaan propagasi.

Untuk mengatasi penundaan pada ripple carry adder, diperkenalkanlah carry-lookahead adder. Di sini, dengan menggunakan perangkat keras yang rumit, penundaan propagasi dapat diminimalkan. Diagram di bawah ini menunjukkan penambah carry-lookahead menggunakan penambah penuh.

Carry Lookahead Menggunakan Full Adder

Tabel kebenaran dan persamaan keluaran yang sesuai adalah

| UNTUK | B | C | C + 1 | Kondisi |

| 0 | 0 | 0 | 0 | Tanpa Carry Menghasilkan |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Tanpa Carry Menyebarkan |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Membawa Menghasilkan |

| 1 | 1 | 1 | 1 |

Persamaan carry propagates adalah Pi = Ai XOR Bi dan carry generate adalah Gi = Ai * Bi. Dengan persamaan ini, persamaan sum dan carry dapat direpresentasikan sebagai

JUMLAH = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi mengirimkan carry hanya jika input Ai dan Bi bernilai 1 tanpa mempertimbangkan input carry. Pi terkait dengan propagasi carry dari Ci ke Ci + 1.

Perbedaan antara Half Adder dan Full Adder

Itu perbedaan antara tabel penambah setengah dan penambah penuh ditampilkan di bawah.

| Half Adder | Adder penuh |

| Half Adder (HA) adalah rangkaian logika kombinasional dan rangkaian ini digunakan untuk menambahkan dua digit satu-bit. | Full Adder (FA) adalah rangkaian kombinasional dan rangkaian ini digunakan untuk menjumlahkan tiga digit satu bit. |

| Di HA, setelah carry dibuat dari penambahan sebelumnya tidak dapat ditambahkan ke langkah berikutnya. | Di FA, setelah carry dihasilkan dari penambahan sebelumnya, maka bisa ditambahkan ke langkah berikutnya. |

| Setengah penambah mencakup dua gerbang logika seperti gerbang AND dan gerbang EX-OR. | Penambah penuh mencakup dua gerbang EX-OR, dua gerbang OR, dan dua gerbang AND. |

| Bit input di setengah penambah adalah dua seperti A, B. | Bit input dalam penambah penuh ada tiga seperti A, B & C-in |

| Persamaan penjumlahan setengah dan bawa adalah S = a⊕b C = a * b | Ekspresi logika adder penuh adalah S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA digunakan di komputer, kalkulator, perangkat yang digunakan untuk pengukuran digital, dll. | FA digunakan dalam prosesor digital, penambahan banyak bit, dll. |

Itu perbedaan utama antara half adder dan full adder dibahas di bawah.

- Half adder menghasilkan sum & carry dengan menambahkan dua input biner sedangkan full adder digunakan untuk menghasilkan sum & carry dengan menambahkan tiga input biner. Baik arsitektur perangkat keras penambah setengah dan penambah penuh tidak sama.

- Fitur utama yang membedakan HA & FA adalah bahwa di HA tidak ada kesepakatan untuk mempertimbangkan penambahan terakhir seperti inputnya. Tapi, FA menempatkan kolom input tertentu seperti Cin untuk mempertimbangkan bit carry tambahan terakhir.

- Kedua penambah akan menunjukkan perbedaan berdasarkan komponen yang digunakan pada rangkaian untuk konstruksinya. Setengah penambah (HA) dirancang dengan kombinasi dua gerbang logika seperti AND & EX-OR sedangkan FA dirancang dengan kombinasi tiga gerbang AND, dua gerbang XOR & satu OR.

- Pada dasarnya, HA beroperasi pada 2-dua input 1-bit, sedangkan FA beroperasi pada tiga input 1-bit. Penambah setengah digunakan dalam perangkat elektronik yang berbeda untuk mengevaluasi penambahan sedangkan penambah penuh digunakan dalam prosesor digital untuk penambahan bit panjang.

- Persamaan dalam dua penambah ini adalah, baik HA & FA adalah rangkaian digital kombinasional sehingga, mereka tidak menggunakan elemen memori apa pun seperti rangkaian sekuensial. Sirkuit ini penting untuk operasi aritmatika untuk memberikan penjumlahan bilangan biner.

Implementasi Full Adder menggunakan Half Adders

Penerapan FA dapat dilakukan melalui dua setengah penambah yang terhubung secara logis. Diagram blok ini dapat ditunjukkan di bawah ini yang memberi tahu koneksi FA menggunakan dua penjumlah setengah.

Jumlah dan persamaan carry dari perhitungan sebelumnya adalah

S = A 'B' Cin + A 'BC' di + ABCin

Cout = AB + ACin + BCin

Persamaan penjumlahan dapat ditulis sebagai.

Cin (A’B '+ AB) + C' in (A'B + A B ')

Jadi, Jumlah = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C’in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Cout bisa ditulis seperti berikut.

COUT = AB + ACin + BCin.

COUT = AB + + kekecewaan BCin (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ') + A ’B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB ’Cin + A’ B Cin

= AB + Cin (AB ’+ A’B)

Oleh karena itu, COUT = AB + Cin (A EX-OR B)

Bergantung pada dua persamaan penjumlahan & carry di atas, sirkuit FA dapat diimplementasikan dengan bantuan dua gerbang HAs & gerbang OR. Diagram rangkaian penambah penuh dengan dua penjumlah setengah diilustrasikan di atas.

Full Adder menggunakan Two Half Adders

Full Adder Design dengan menggunakan NAND Gates

Gerbang NAND adalah salah satu jenis gerbang universal, digunakan untuk menjalankan segala jenis desain logika. Sirkuit FA dengan diagram gerbang NAND ditunjukkan di bawah ini.

FA menggunakan NAND Gates

FA adalah penambah satu-bit yang mudah dan jika kita ingin mengeksekusi penambahan n-bit, maka n no. FA satu-bit harus digunakan dalam format koneksi kaskade.

Keuntungan

Itu keuntungan dari half adder dan full adder termasuk yang berikut ini.

- Tujuan utama dari setengah penjumlah adalah untuk menambahkan dua angka bit tunggal

- Penambah penuh memiliki kemampuan untuk menambahkan bit pembawa yang merupakan hasil dari penambahan sebelumnya

- Dengan full adder, rangkaian krusial seperti adder, multiplexer, dan banyak lainnya dapat diimplementasikan

- Sirkuit penambah penuh mengkonsumsi daya minimal

- Keuntungan dari penambah penuh lebih dari penambah setengah adalah, penambah penuh digunakan untuk mengatasi kekurangan penambah setengah karena penambah setengah terutama digunakan untuk menambahkan dua nomor 1-bit. Setengah penambah tidak menambahkan bit pembawa, jadi untuk mengatasi penambah penuh ini digunakan. Pada Full adder, penambahan tiga bit dapat dilakukan dan menghasilkan dua keluaran.

- Mendesain penambah sederhana dan merupakan blok bangunan dasar sehingga penjumlahan satu bit dapat dengan mudah dipahami.

- Penambah ini dapat diubah menjadi setengah pengurang dengan menambahkan inverter.

- Dengan menggunakan full adder, output yang tinggi bisa didapatkan.

- Kecepatan tinggi

- Sangat kuat untuk memasok penskalaan tegangan

Kekurangan

Itu kekurangan setengah penambah dan penambah penuh termasuk yang berikut ini.

- Selain itu, setengah penambah tidak dapat digunakan sebelum dibawa, sehingga tidak dapat digunakan untuk menambahkan multi-bit secara bertahap.

- Untuk mengatasi kekurangan ini, FA perlu menambahkan tiga 1 bit.

- Setelah FA digunakan dalam bentuk rantai seperti RA (Ripple Adder), maka output kapabilitas drive dapat diturunkan.

Aplikasi

Aplikasi setengah penambah dan penambah penuh meliputi yang berikut ini.

- Penambahan bit biner dapat dilakukan dengan half adder menggunakan ALU di dalam komputer karena menggunakan adder.

- Kombinasi setengah penambah dapat digunakan untuk mendesain rangkaian penambah penuh.

- Setengah penjumlah digunakan dalam kalkulator dan untuk mengukur alamat serta tabel

- Sirkuit ini digunakan untuk menangani berbagai aplikasi dalam sirkuit digital. Di masa depan, ini memainkan peran kunci dalam elektronik digital.

- Sirkuit FA digunakan sebagai elemen di banyak sirkuit besar seperti Ripple Carry Adder. Penambah ini menambahkan jumlah bit secara bersamaan.

- FA digunakan dalam Arithmetic Logic Unit (ALU)

- FA digunakan dalam aplikasi yang berhubungan dengan grafik seperti GPU (Graphics Processing Unit)

- Ini digunakan dalam rangkaian perkalian untuk menjalankan Perkalian Carryout.

- Di komputer, untuk menghasilkan alamat memori & untuk membangun program counterpoint menuju instruksi selanjutnya, Unit Logika Aritmatika digunakan dengan menggunakan Penambah Penuh.

Jadi, setiap kali dilakukan penambahan dua bilangan biner maka digit-digit tersebut ditambahkan pada bit terkecil terlebih dahulu. Proses ini dapat dilakukan melalui penjumlahan setengah karena n / w paling sederhana yang memungkinkan penambahan dua bilangan 1-bit. Input dari penjumlah ini adalah digit biner sedangkan outputnya adalah penjumlahan (S) & carry (C).

Kapanpun jumlah digit dimasukkan, maka jaringan HA digunakan hanya untuk menghubungkan digit terkecil, karena HA tidak dapat menambahkan nomor carry dari kelas sebelumnya. Penambah penuh dapat didefinisikan sebagai basis dari semua perangkat aritmatika digital. Ini digunakan untuk menambahkan tiga angka 1 digit. Penambah ini mencakup tiga input seperti A, B, dan Cin sedangkan outputnya adalah Sum dan Cout.

Konsep Terkait

Itu konsep yang terkait dengan setengah penambah dan penambah penuh hanya tidak terpaku pada satu tujuan. Mereka memiliki penggunaan ekstensif di banyak aplikasi dan beberapa yang terkait disebutkan:

- Nomor IC penambah setengah dan penambah penuh

- Pengembangan penambah 8-bit

- Apakah tindakan pencegahan setengah penambah?

- Applet JAVA dari Ripple Carry Adder

Oleh karena itu, ini semua tentang teori penambah setengah dan penambah penuh beserta tabel kebenaran dan diagram logika, desain full adder menggunakan rangkaian half adder juga ditampilkan. Banyak dari setengah penambah dan penambah penuh pdf dokumen tersedia untuk memberikan informasi lanjutan tentang konsep ini. Lebih jauh lagi penting untuk diketahui bagaimana penambah penuh 4-bit diterapkan ?