Proses perancangan perangkat keras digital telah berubah secara intens selama beberapa tahun terakhir. Jadi, sirkuit digital kecil dapat diimplementasikan dengan menggunakan PAL dan PLA. Setiap perangkat digunakan untuk mengimplementasikan berbagai sirkuit yang tidak membutuhkan lebih dari jumlah i / ps, o / ps dan persyaratan produk yang ditawarkan dalam chip tertentu. Chip ini tidak memadai untuk ukuran yang cukup sederhana, biasanya mendukung jumlah input dan output yang saling menguntungkan tidak lebih dari 32. Untuk mendesain sirkuit ini yang membutuhkan lebih banyak input dan output, sejumlah PLA / PAL dapat digunakan atau jenis yang lebih berkelas chip dapat digunakan disebut CPLD (perangkat logika yang dapat diprogram kompleks). Chip CPLD mencakup beberapa blok sirkuit pada satu chip dengan sumber daya kabel di dalam untuk memasang blok sirkuit. Setiap blok sirkuit sebanding dengan PLA atau PAL.

Apa itu Perangkat Logika yang Dapat Diprogram Kompleks?

Singkatan dari CPLD adalah 'Perangkat logika yang dapat diprogram kompleks', ini adalah satu jenis sirkuit terintegrasi Desainer aplikasi itu mendesain untuk mengimplementasikan perangkat keras digital seperti ponsel. Ini dapat menangani desain yang diketahui lebih tinggi daripada SPLD (perangkat logika yang dapat diprogram sederhana), tetapi menawarkan logika yang lebih sedikit daripada FPGA ( bidang array gerbang yang dapat diprogram ). CPLD menyertakan banyak blok logika yang masing-masing blok mencakup 8-16 sel makro. Karena setiap blok logika menjalankan fungsi tertentu, semua sel makro dalam blok logika terhubung sepenuhnya. Tergantung pada penggunaannya, blok-blok ini mungkin atau mungkin tidak terhubung satu sama lain.

Perangkat Logika yang Dapat Diprogram Kompleks

Kebanyakan CPLD (perangkat logika terprogram kompleks) memiliki sel makro dengan sejumlah fungsi logika dan elektif FF (flip-flop) . Bergantung pada chipnya, fungsi logika kombinatorial mendukung dari 4 hingga 16 istilah produk dengan fan-in inklusif. CPLD juga berbeda dalam hal register geser dan gerbang logika. Karena alasan ini, CPLD dengan sejumlah besar gerbang logika dapat digunakan sebagai pengganti FPGA. Spesifikasi CPLD lain menandakan jumlah istilah produk yang dapat dicapai oleh sel makro. Istilah produk adalah produk sinyal digital yang menjalankan fungsi logika tertentu.

CPLD tersedia dalam beberapa bentuk paket IC dan keluarga logika. CPLD juga berbeda dalam hal tegangan suplai, arus operasi, arus siaga, dan disipasi daya. Selain itu, ini dapat diperoleh dengan berbagai jumlah memori dan berbagai jenis dukungan memori. Biasanya, memori diekspresikan dalam bit / megabit. Dukungan memori terdiri dari ROM, RAM, dan RAM port ganda. Ini juga terdiri dari memori CAM (memori beralamat konten) serta FIFO (first-in, first-out) dan memori LIFO (last-in, last-out).

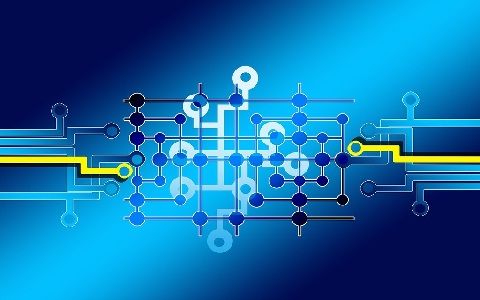

Arsitektur Perangkat Logika yang Dapat Diprogram Kompleks

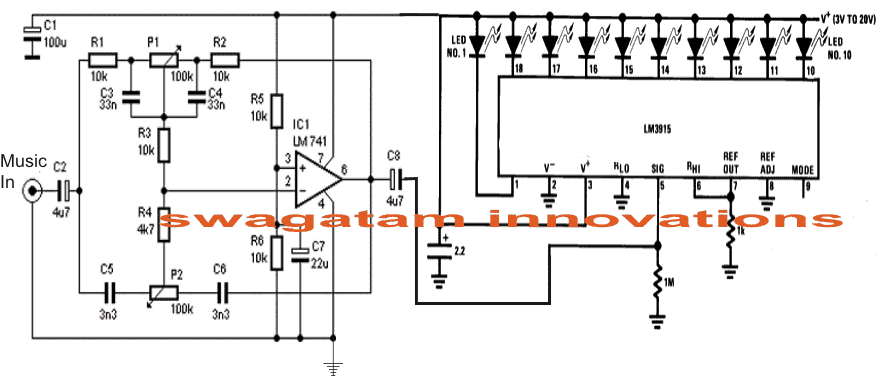

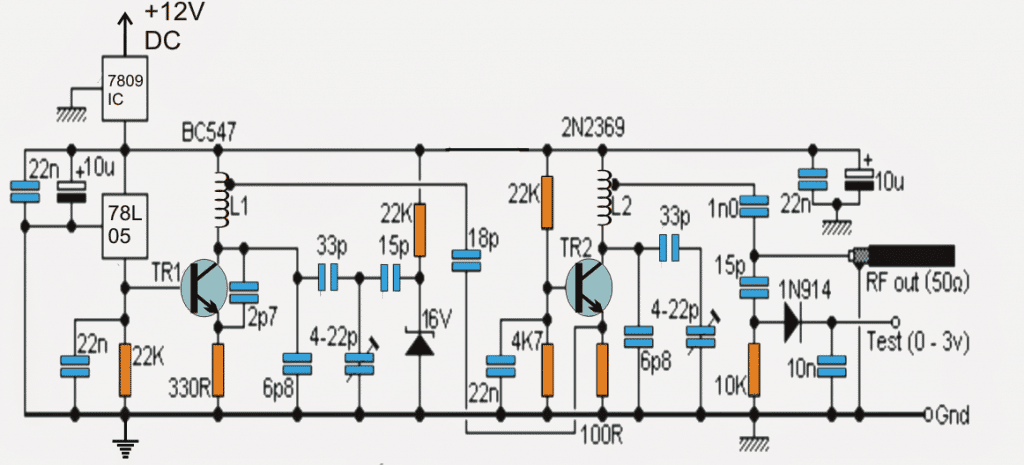

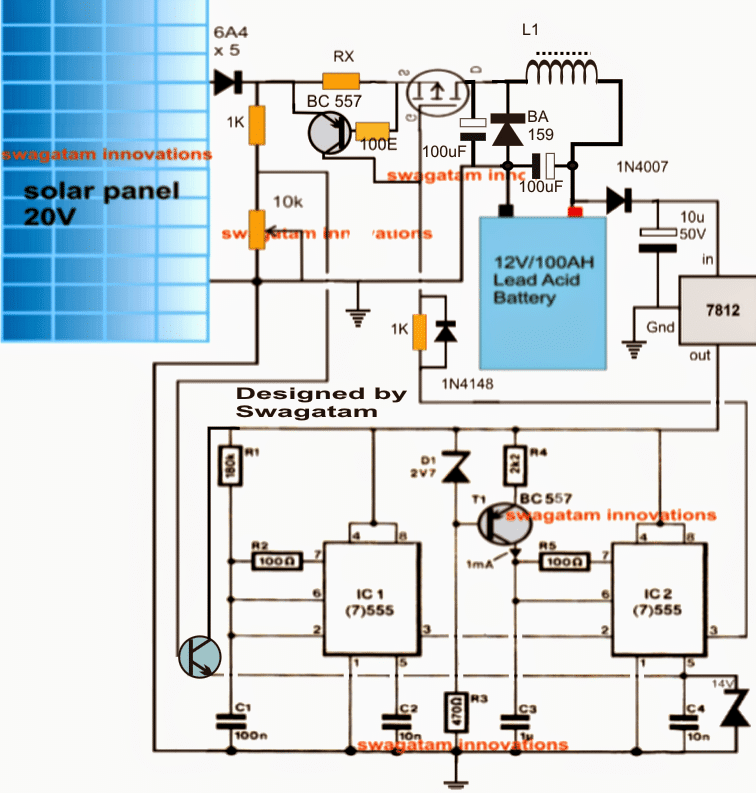

Perangkat logika yang dapat diprogram kompleks terdiri dari sekelompok FB yang dapat diprogram (blok fungsional). Input dan output dari blok fungsional ini dihubungkan bersama oleh GIM (matriks interkoneksi global). Matriks interkoneksi ini dapat dikonfigurasi ulang, sehingga kita dapat memodifikasi kontak antar blok fungsional. Akan ada beberapa blok input dan output yang memungkinkan kita untuk menyatukan CPLD ke dunia luar. Arsitektur CPLD ditunjukkan di bawah ini.

Umumnya, FB yang dapat diprogram terlihat seperti file berbagai gerbang logika , di mana sebuah array gerbang AND dapat diprogram dan gerbang OR stabil. Tapi, setiap pabrikan memiliki cara berpikir mereka sendiri untuk merancang blok fungsional. Output daya yang terdaftar dapat ditemukan dengan mengoperasikan sinyal umpan balik yang diperoleh dari output gerbang OR.

Arsitektur CPLD

Dalam pemrograman CPLD, desain pertama kali dikodekan dalam bahasa Verilog atau VHDL setelah kode tersebut (disimulasikan dan disintesis. Selama sintesis, model CPLD (perangkat target) dipilih sendiri dan daftar jaring pemetaan berbasis teknologi dihasilkan. Daftar ini dapat ditutup -sesuai dengan arsitektur CPLD asli menggunakan proses tempat dan rute, biasanya dicapai oleh perangkat lunak tempat-dan-rute milik Perusahaan CPLD. Kemudian operator akan melakukan beberapa proses konfirmasi. Jika semuanya baik-baik saja, dia akan menggunakan CPLD, jika tidak dia akan mengatur ulang itu.

Masalah Arsitektur CPLD

Saat mempertimbangkan perangkat logika terprogram yang kompleks untuk digunakan dalam desain, ada beberapa masalah arsitektur berikut yang dapat dipertimbangkan

- Teknologi pemrograman

- Kemampuan blok fungsi

- Kemampuan I / O

Beberapa keluarga CPLD dari pengecer berbeda termasuk

- Altera MAX 7000 dan MAX 9000 keluarga

- Keluarga Atmel ATF dan ATV

- Keluarga LSI ISP kisi

- Keluarga Lattice (Vantis) MACH

- Keluarga Xilinx XC9500

Keluarga CPLD

Aplikasi CPLD

Aplikasi CPLD meliputi berikut ini

- Perangkat logika yang dapat diprogram kompleks ideal untuk kinerja tinggi, aplikasi kontrol kritis.

- CPLD dapat digunakan dalam desain digital untuk menjalankan fungsi boot loader

- CPLD digunakan untuk memuat data konfigurasi dari array gerbang yang dapat diprogram lapangan dari memori non-volatile.

- Umumnya, ini digunakan dalam aplikasi desain kecil seperti decoding alamat

- CPLD sering digunakan dalam banyak aplikasi seperti perangkat portabel yang sensitif biaya dan dioperasikan dengan baterai karena ukurannya yang rendah dan penggunaan daya yang rendah.

Jadi, ini semua tentang arsitektur perangkat logika terprogram yang kompleks dan aplikasinya. Kami berharap Anda mendapatkan pemahaman yang lebih baik tentang konsep ini. Selanjutnya, setiap pertanyaan tentang konsep ini atau untuk melaksanakan proyek listrik dan elektronik , tolong berikan saran berharga Anda dengan berkomentar di bagian komentar di bawah. Berikut pertanyaan untuk Anda, apa perbedaan antara CPLD dan FPGA?

Kredit Foto:

- CPLD wikimedia

- Arsitektur CPLD slidesharecdn